### 3 高出力増幅器

#### 3.1 高出力化

##### 3.1.1 増幅器の高出力化設計

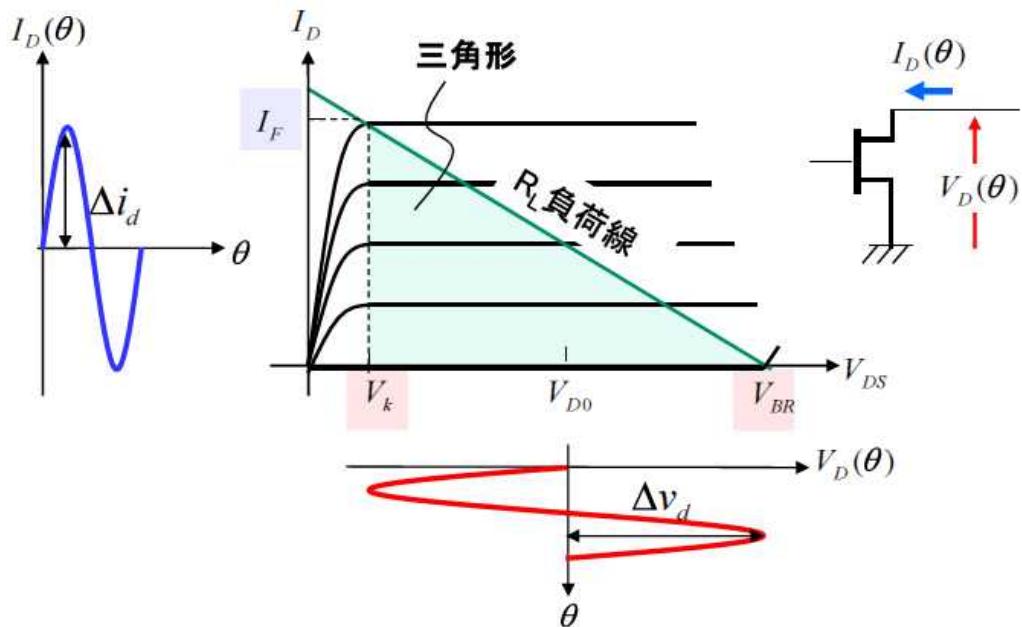

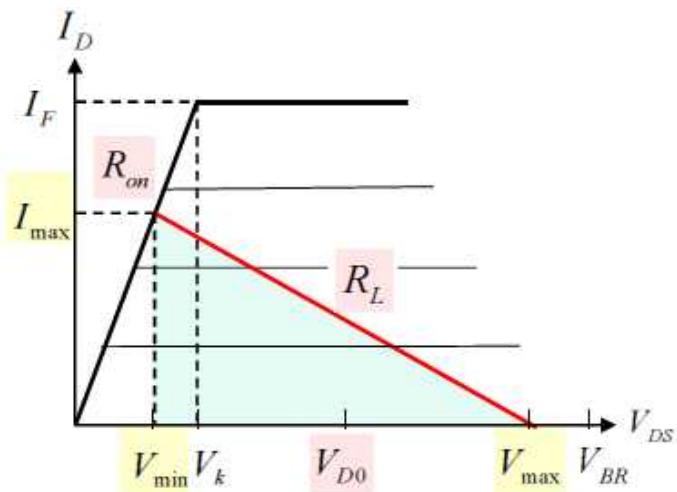

図3.1にFETの静特性とRF電流  $I_D(\theta)$ ， 電圧  $V_D(\theta)$  の関係を示す。

図3.1 FETの静特性とRF電流，電圧の関係

このFETから得られる最大RF出力電力  $P_{out,max}$  は，  $\Delta i_d = \frac{I_F}{2}$ ，  $\Delta v_d = \frac{V_{BR} - V_k}{2}$  の時に得られ， 次式で与えられる。

$$P_{out,max} = \frac{1}{8} I_F \cdot (V_{BR} - V_k) \approx \frac{1}{8} I_F \cdot V_{BR} \quad (3.1)$$

ここで、 $I_F$  は最大ドレン電流、 $V_{BR}$  はブレークダウン電圧、 $V_k$  はニードル電圧である。出力電力は、図3.1に示された三角形の面積に比例しており、高出力化はこの面積を大きくすることともいえる。以下で  $I_F$  と  $V_{BR}$  の増大による高出力化について述べる。

### (a) $I_F$ の増大

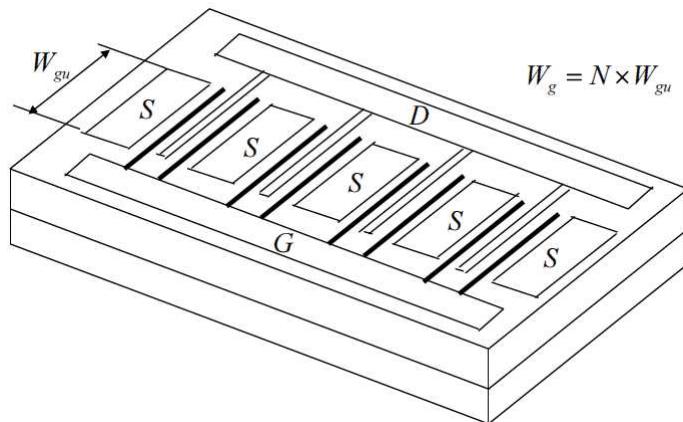

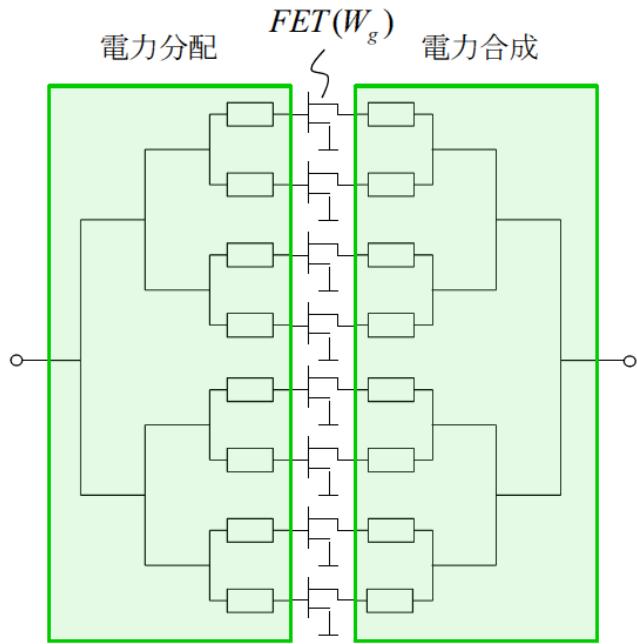

$I_F$  の増大を図るには、FETのゲート幅  $W_g$  を増大すれば良い。このためには、図3.2のFET構造において、単位ゲート幅  $W_{gu}$  およびゲート本数  $N$  を増大すればよい。しかし、 $W_{gu}$  および  $N$  を単純に増大しFET寸法が大きくなると、FETは均一動作しなくなり、利得、出力が効率よく引き出せなくなる問題が生じる。このためFET寸法、すなわちゲート幅  $W_g = N \times W_{gu}$  には適切な値があり、1つのFET（セルあるいはチップ）から引き出せる出力には限度がある。このため、さらに高出力化を図るには、図3.3のようにゲート幅  $W_g$  のFET（セルあるいはチップ）を複数個並列動作させ、その出力を合成回路により効率よく合成することが必要である。

図3.2 FETの構造（ゲート幅  $W_g = N \times W_{gu}$ ）

図3.3 並列動作する複数個のFET ( $W_g$ ) の電力合成

### (b) $V_{BR}$ の増大

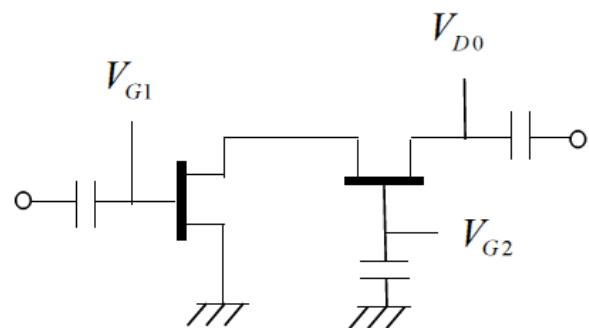

$V_{BR}$  の増大のため、一般には高耐圧デバイス（例えばGaN HFET等）の採用がある。しかし、CMOS FET（CMOS LSIプロセスで作られたMOS FETをここではCMOS FETと呼ぶ）のように耐圧の低いデバイスを使わざるを得ないときもある。このような時、カスコード接続したFET構成とすることで、見かけの耐圧を高めることができる。図3.4にカスコード接続FETの回路構成を示す。

図3.4 カスコード接続FETの回路構成

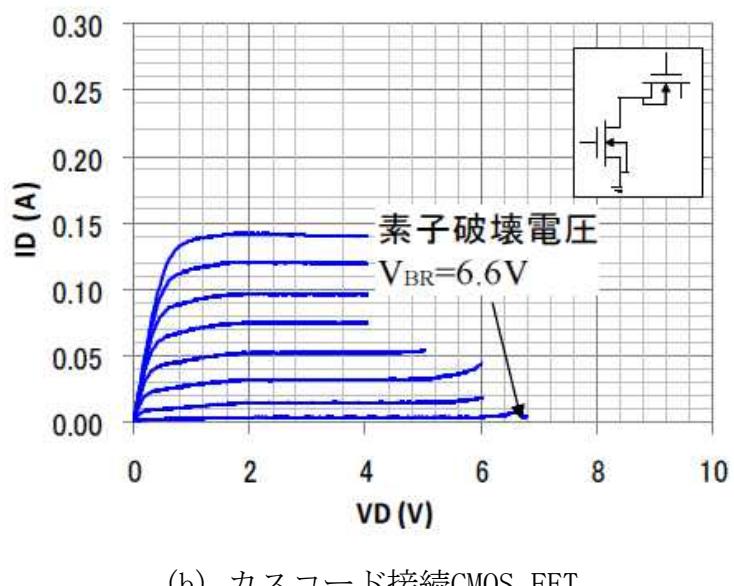

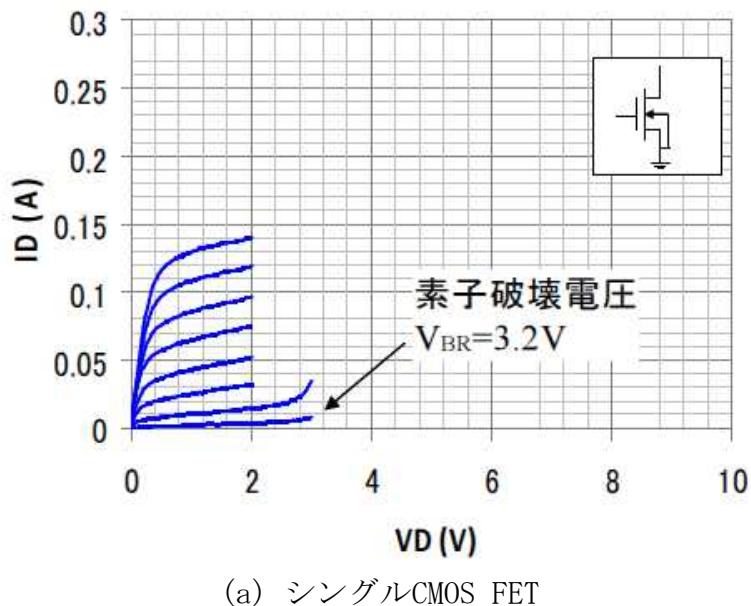

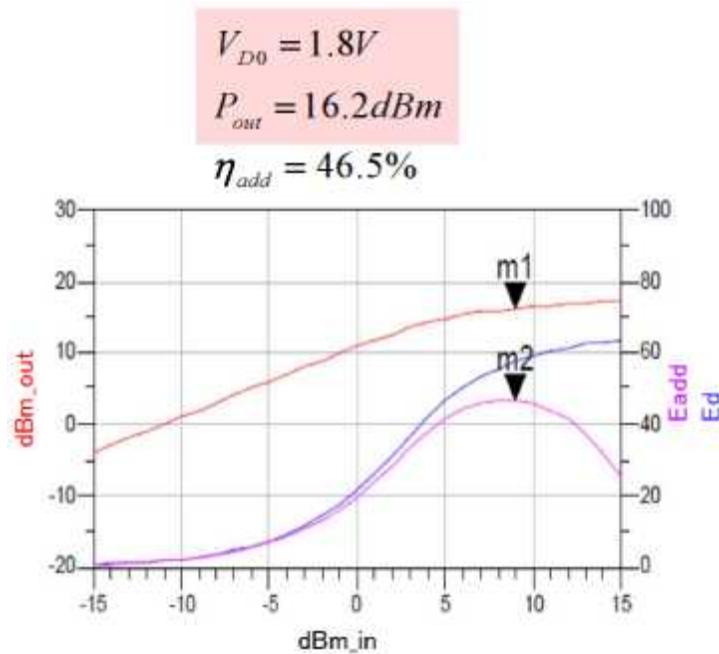

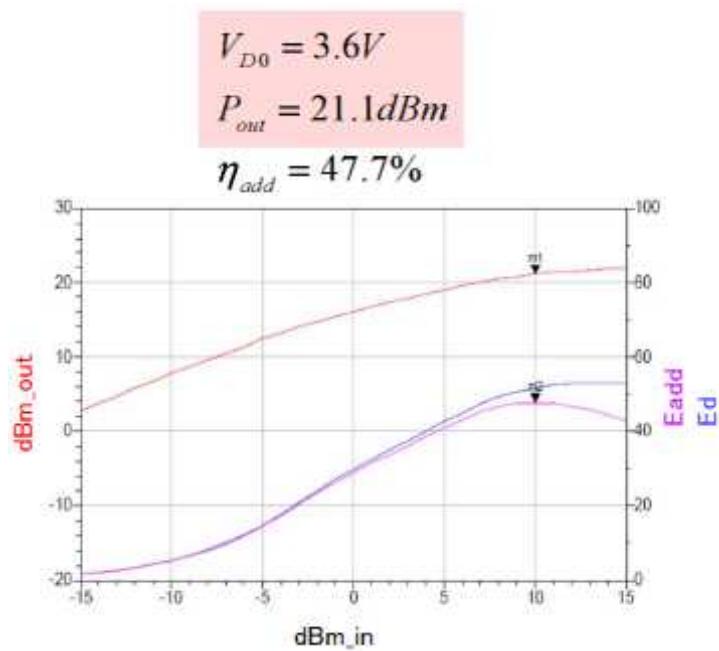

図3.5に、(a) シングルCMOS FET, (b) カスコード接続CMOS FET の静特性測定結果を示す。カスコード接続構成により見かけの耐圧を向上できることがわかる。図3.6に (a) シングルCMOS FET増幅器, (b) カスコード接続CMOS FET増幅器の5GHzにおける入出力特性シミュレーション結果を示す。カスコード接続構成とすることで出力も増大している（実験においても確認されている）。

図3.5 CMOS FET の静特性（測定）

～カスコード接続による耐圧向上～

(a) シングルCMOS FET増幅器

(b) カスコード接続CMOS FET増幅器

図3.6 CMOS FET 増幅器の入出力特性 (5GHz シミュレーション)

～カスコード接続による出力向上～

### 3.1.2 電力合成とループ発振<sup>[1]</sup>

FET 増幅器の高出力化を図るため、FET を並列に接続しその出力を合成する場合、各 FET とこれを接続する回路とからなる閉ループ内で発振（以後ループ発振とよぶ）の生じることがある。本節では、ループ発振の発生メカニズムについて述べ、発振条件を導出するとともに、一般の並列動作 FET 増幅器の場合にループ発振条件および発振周波数を計算する方法について述べる。また、ループ発振を防止するのにアイソレーション抵抗を装荷することが有効であることを示す。

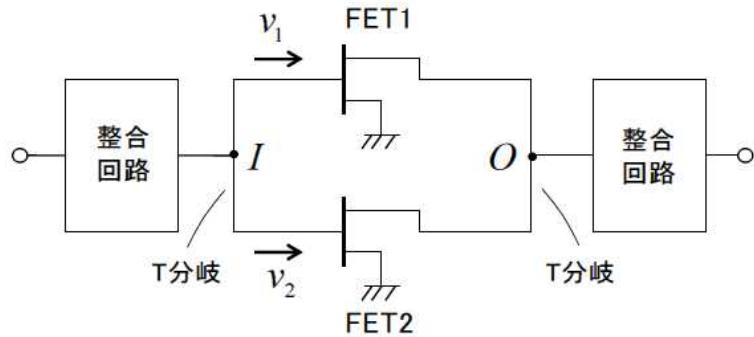

ここではまず、図 3.7 に示すように、2 個の FET（または、入出力回路の一部を含む FET 回路）が T 分岐で接続されている簡単な構成の場合について考える。ここで、FET1, FET2 の特性は同一であるとする。このような 2 つの回路からなる系の電磁界の一般解は、偶モードと奇モード電磁界の重ね合わせとして与えられる。

図 3.7 並列動作 FET 増幅器の構成

(2 個の FET が T 分岐で接続されている)

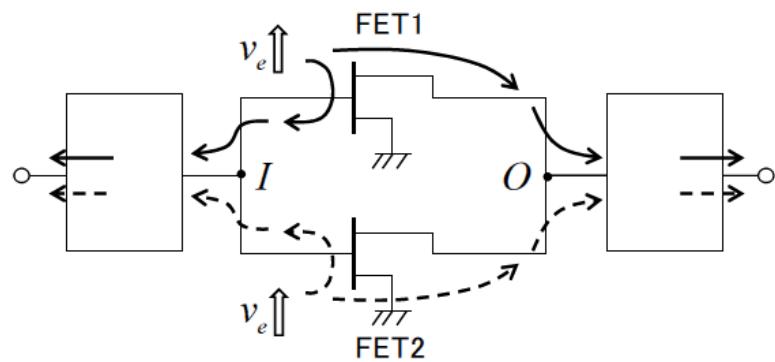

図 3.8 に偶モード進行波  $v_e$  の伝搬の様子を示す。偶モードでは、FET で増幅された波は図の  $O$  点で同相、等振幅でたし合わされ出力端子側に出力される。また、FET の入力側で反射された波は図の  $I$  点で同相、等振幅でたし合わされ入力端子側に出力される。これから、偶モード成分にもとづく発振の有無は通常の単一 FET の場合と同様に安定係数  $K$  により判定される。

図 3.9 に奇モード進行波  $v_o$  の伝搬の様子を示す。奇モードでは、FET で増幅された波は図の  $O$  点で逆相、等振幅でたし合わされることになり  $O$  点で電圧が

ゼロになり等価的に短絡となる。このため、 $O$ 点で位相が $180^\circ$ 反転して全反射される。また、FETの入力側で反射された波は、 $I$ 点で逆相、等振幅でたし合わされることになり $I$ 点は等価的に短絡となる。このため、 $I$ 点で位相が $180^\circ$ 反転して全反射される。別の見方をすると、奇モード成分の波は図の実線または破線のようにT分岐外部の影響を受けずにそのまま並列動作している他方のFET側に伝搬していくとみることも出来る。ループ発振は回路中に存在する雑音による微小電圧が図3.9の実線あるいは破線で示すようなループを描いて伝搬するうちに成長するために生じると考えられる。

図3.8 偶モード進行波 $v_e$ の伝搬の様子

図3.9 奇モード進行波 $v_o$ の伝搬の様子

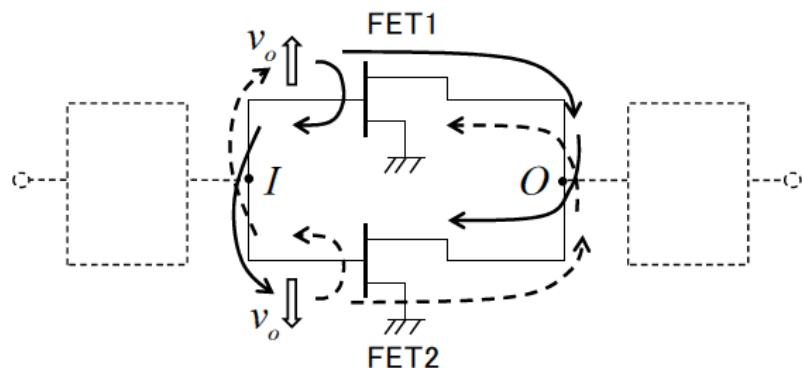

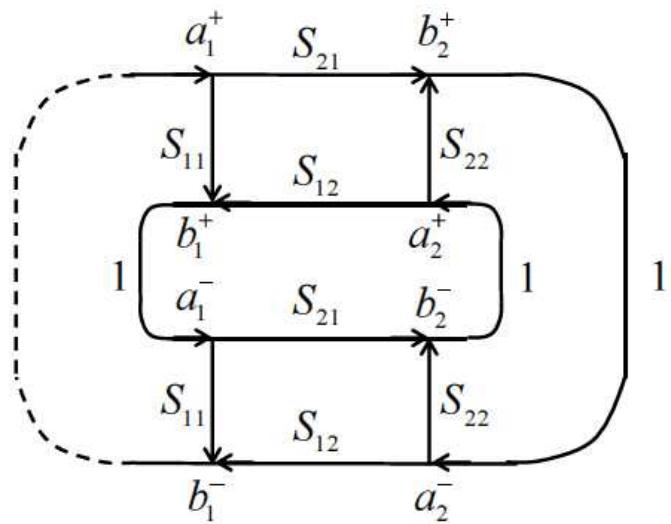

図3.9の奇モード進行波のうちの例えれば実線のループを形成する進行波を表

わすシグナルフローグラフは図 3.10 のようになる。

図 3.10 ループを形成する進行波を表わすシグナルフローグラフ

図 3.10において、初めに  $a_1^+$  が存在したとして、 $b_1^-$  を  $a_1^+$  と  $S$  パラメータ  $S_{ij}$

の関数として表わす。同様のことを  $a_2^+$ ,  $a_1^-$ ,  $a_2^-$  について行うと次式が得られる。

$$\frac{b_1^-}{a_1^+} = \frac{b_1^+}{a_1^-} = f(S_{ij}) \quad (3.2)$$

$$\frac{b_2^-}{a_2^+} = \frac{b_2^+}{a_2^-} = g(S_{ij}) \quad (3.3)$$

ただし、

$$f(S_{ij}) = \frac{2S_{11}S_{22}S_{12}S_{21} - S_{11}^2S_{22}^2 - S_{12}^2S_{21}^2 + S_{12}S_{21} + S_{11}^2}{1 - S_{12}S_{21} - S_{22}^2} \quad (3.4)$$

$$g(S_{ij}) = \frac{2S_{11}S_{22}S_{12}S_{21} - S_{11}^2S_{22}^2 - S_{12}^2S_{21}^2 + S_{12}S_{21} + S_{22}^2}{1 - S_{12}S_{21} - S_{11}^2} \quad (3.5)$$

もし、初めに存在した  $a_1^+$  に対して、それから生じる  $b_1^-$  が  $\left| \frac{b_1^-}{a_1^+} \right| \geq 1$ ，かつ，

$\angle \frac{b_1^-}{a_1^+} = 2n\pi$  ( $n$  は整数) であれば、発振は成長する。同様なことが、 $\frac{b_1^+}{a_1^-}$ ,  $\frac{b_2^-}{a_2^+}$

,  $\frac{b_2^+}{a_2^-}$  についてもいえる。これから、ループ発振は以下の条件 A または条件 B のどちらかを満たす時に生じるといえる。

条件 A

$$\left| \frac{b_1^-}{a_1^+} \right| = \left| \frac{b_1^+}{a_1^-} \right| = |f(S_{ij})| \geq 1 \quad \text{かつ} \quad \angle \frac{b_1^-}{a_1^+} = \angle \frac{b_1^+}{a_1^-} = \angle f(S_{ij}) = 2n\pi \quad (3.6)$$

条件 B

$$\left| \frac{b_2^-}{a_2^+} \right| = \left| \frac{b_2^+}{a_2^-} \right| = |g(S_{ij})| \geq 1 \quad \text{かつ} \quad \angle \frac{b_2^-}{a_2^+} = \angle \frac{b_2^+}{a_2^-} = \angle g(S_{ij}) = 2n\pi \quad (3.7)$$

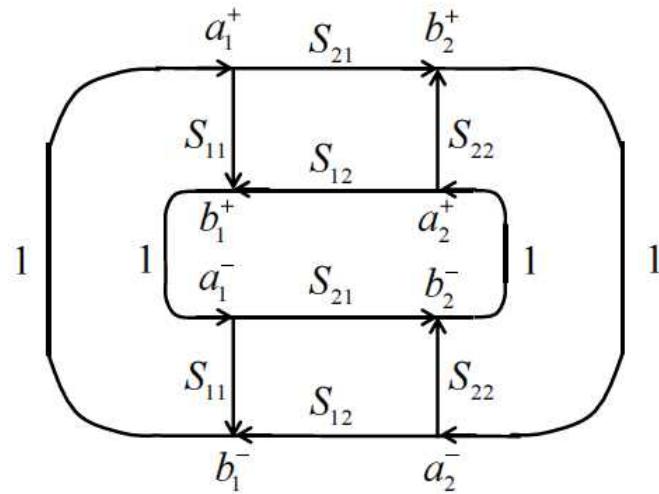

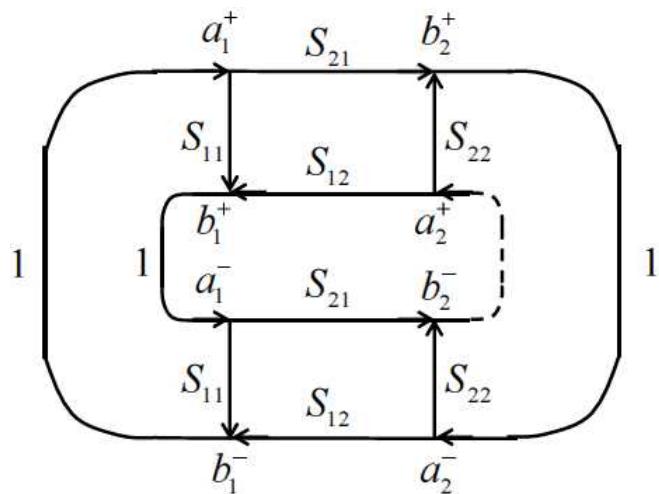

式(3.6), (3.7)から、発振条件を求めることができる。すなわち、条件 A は図

3.11 のシグナルフローグラフにおいて  $\frac{b_1^-}{a_1^+}$  を計算し、式(3.6)に当てはめればよ

く、また条件 B は図 3.11 のシグナルフローグラフにおいて  $\frac{b_2^-}{a_2^+}$  を計算し、式(3.7)

に当てはめればよい。

図 3.11 条件 A を計算するためのシグナルフローグラフ

図 3.12 条件 B を計算するためのシグナルフローグラフ

以上は、FET を含む回路の S パラメータ  $S_{ij}$  があらかじめ得られることを前提として議論を進めたが、回路構成が複雑になると S パラメータ  $S_{ij}$  をあらかじめ計算することは得策ではない。

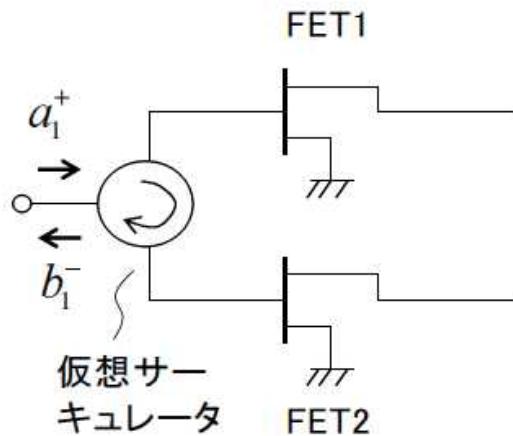

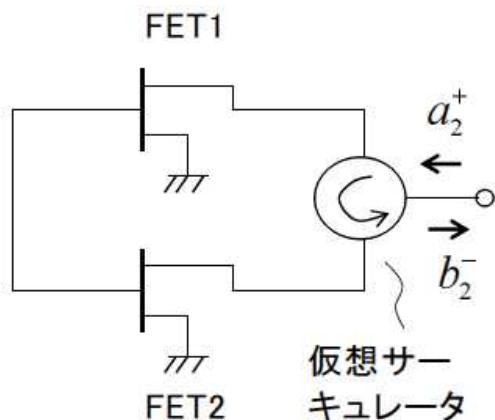

回路構成が比較的複雑となる実際の並列動作 FET 増幅器に市販回路シミュレータを用いてループ発振条件 A, B を計算する方法として、図 3.13, 図 3.14 の回路を用いる方法がある。この方法では、実際に設計された厳密な回路をそのまま

ま用いるとともに、図に示すように仮想サーキュレータを組み合わせ用いることにより、 $\frac{b_1^-}{a_1^+}$ ,  $\frac{b_2^-}{a_2^+}$  を計算する。計算結果を、発振条件を与える式(3.6), 式(3.7)に当てはめればよい。また、この方法を用いると、発振防止のための回路（例えばアイソレーション抵抗）の効果を容易に計算できる利点もある。

図 3.13 仮想サーキュレータを用い発振条件 A を計算する方式

図 3.14 仮想サーキュレータを用い発振条件 B を計算する方式

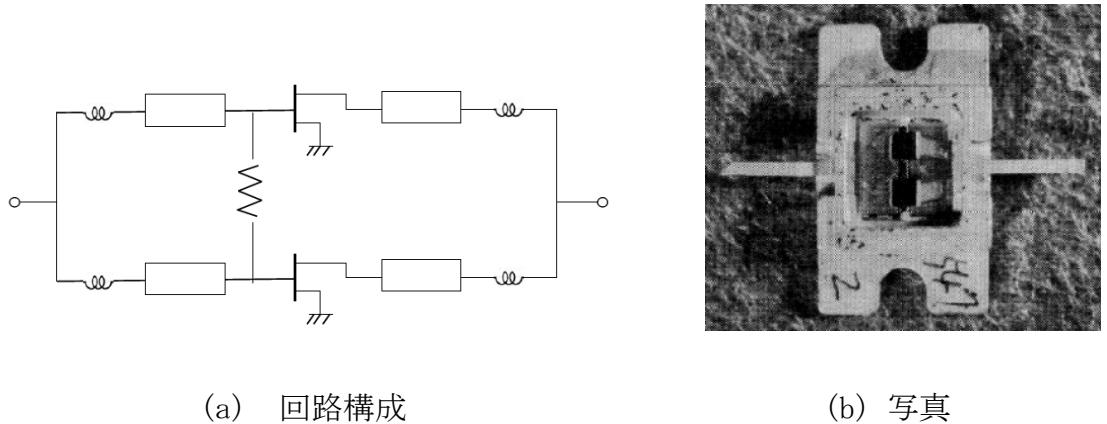

ここで述べたループ発振の解析手法を試作 Ku 帯並列動作 FET 増幅器に適用した例を示す。図 3.15 に増幅器の (a) 回路構成と (b) 写真を示す。2 個の FET チップが並列動作し、パッケージ内のインピーダンス変換を兼ねた分配/合成回路で電力合成される回路となっている。

図 3.15 Ku 帯並列動作 FET 増幅器

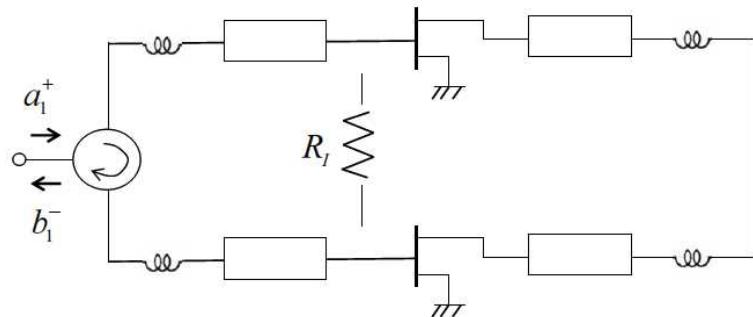

図 3.16 に発振条件 A を計算する回路を示す。アイソレーション抵抗  $R_I$  の有無

に対して  $\frac{b_1^-}{a_1^+}$  を計算した。

図 3.16 発振条件 A を計算する回路

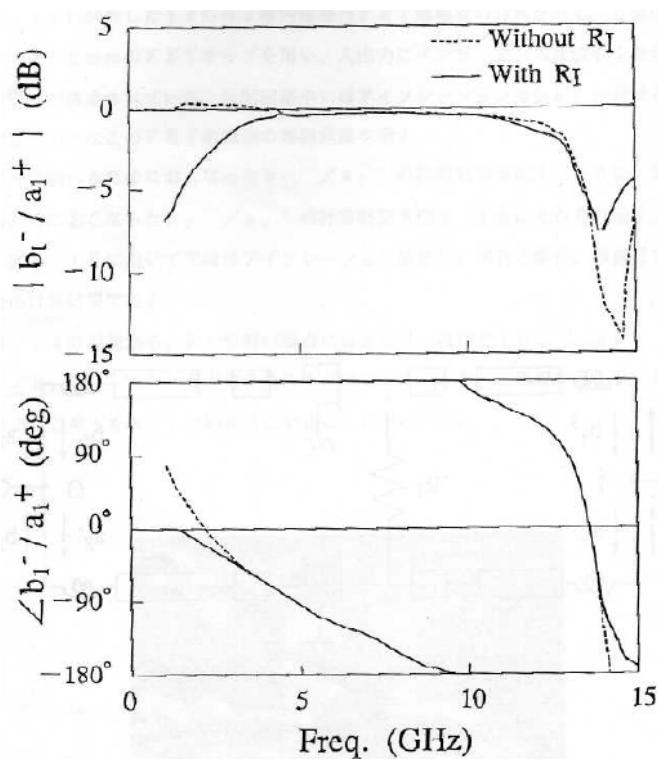

図 3.17 に  $\frac{b_1^-}{a_1^+}$  の計算結果を示す。アイソレーション抵抗  $R_I$  が無い場合（破線）

は、2.5GHz 付近で発振条件 A を満たしている。一方、 $R_I$  を接続した場合（実線）は発振条件を満たさなくなる。

図 3.17 発振条件 A の計算結果

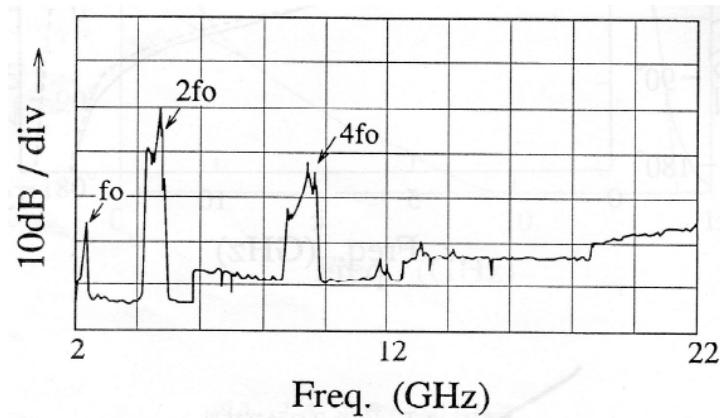

図 3.18 に発振スペクトルの観測結果を示す。 $R_I$  が無い場合 2.5GHz 近傍を基本波とする発振スペクトルが観測される。一方、 $R_I$  を装荷した場合には発振は観測されず、ループ発振を防止できることが確かめられている。

図 3.18 発振スペクトル観測結果

### 3.2 高効率化

FET増幅器の高効率化の方策として、ここでは、(a)効率を最大化する整合回路設計、(b)ゲートバイアス電圧による高効率動作(A→B→C級)、(c)高調波処理による高効率動作(F, F<sup>-1</sup>, E級)について述べる。

#### 3.2.1 出力整合と効率整合

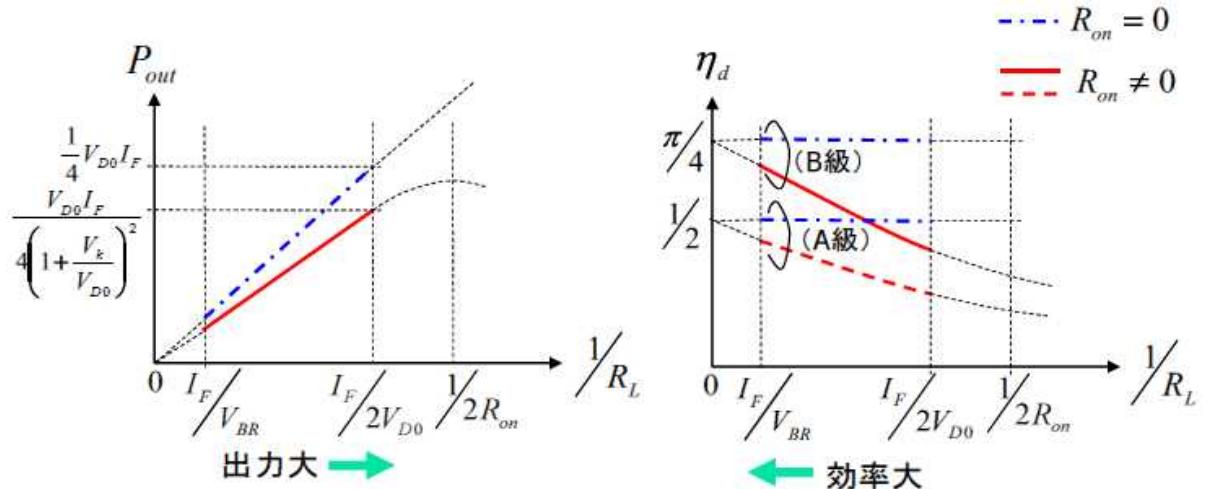

一般に、FETのニードル電圧は  $V_k \neq 0$  であり、オン抵抗も  $R_{on} \neq 0$  である。このようなFETにおいては、出力を最大化する出力整合負荷と効率を最大化する効率整合負荷のインピーダンスが異なってくる<sup>[2]</sup>。図3.19に  $V_k \neq 0$  ( $R_{on} \neq 0$ ) のFETの、静特性、ドレインバイアス電圧  $V_{D0}$ 、負荷インピーダンス  $R_L$  (実数とする) の関係を示す。

図3.19  $V_k \neq 0$  を考慮した静特性と  $V_{D0}$  と  $R_L$

この時、RF出力電力  $P_{out}$ 、直流入力電力  $P_{DC}$ 、ドレイン効率  $\eta_d$  は、図中の  $I_{max}$ 、 $V_{min}$ 、 $V_{max}$  を用いて、以下のように与えられる。

$$P_{out} = \frac{1}{8} I_{\max} (V_{\max} - V_{\min}) \quad (3.8)$$

$$P_{DC} = \frac{1}{\pi} I_{\max} V_{D0} \quad (\text{B級バイアスの場合}) \quad (3.9)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = \frac{\pi}{8} \frac{(V_{\max} - V_{\min})}{V_{D0}} \quad (\text{B級バイアスの場合}) \quad (3.10)$$

ここで、図中の  $I_{\max}$ ,  $V_{\min}$ ,  $V_{\max}$  と  $R_{on}$ ,  $R_L$ ,  $V_{D0}$  とは次式で関係付けられる。

$$\left. \begin{aligned} R_{on} &= \frac{V_{\min}}{I_{\max}} \\ R_L &= \frac{V_{\max} - V_{\min}}{I_{\max}} \\ V_{D0} &= \frac{1}{2}(V_{\max} + V_{\min}) \end{aligned} \right\} \quad (3.11)$$

連立式(3.11)を解いて、 $I_{\max}$ ,  $V_{\min}$ ,  $V_{\max}$  は以下のように与えられる。

$$\left. \begin{aligned} I_{\max} &= \frac{2V_{D0}}{R_L + 2R_{on}} \\ V_{\min} &= \frac{2V_{D0}R_{on}}{R_L + 2R_{on}} \\ V_{\max} &= \frac{2V_{D0}(R_L + R_{on})}{R_L + 2R_{on}} \end{aligned} \right\} \quad (3.12)$$

上式 (3.12) の結果を式 (3.8) ~ (3.10) に代入することで  $P_{out}$ ,  $P_{DC}$ ,  $\eta_d$  は、以下のように与えられる。

$$P_{out} = \frac{V_{D0}^2}{2R_L} \frac{1}{\left(1 + \frac{2R_{on}}{R_L}\right)^2} \quad (3.13)$$

$$P_{DC} = \frac{2}{\pi} \frac{V_{D0}^2}{R_L + 2R_{on}} \quad (\text{B級バイアスの場合}) \quad (3.14)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = \frac{\pi}{4} \frac{1}{\left(1 + \frac{2R_{on}}{R_L}\right)} \quad (\text{B級バイアスの場合}) \quad (3.15)$$

図3.20に  $R_L$  に対する  $P_{out}$  と  $\eta_d$  の特性を示す。図には、A級およびB級動作について示す。また比較のため、 $R_{on} \neq 0$  の場合と  $R_{on} = 0$  の場合についても示す。図から、 $R_{on} \neq 0$  の場合、回路設計的には  $R_L$  を大きくする ( $1/R_L$  を小さくする) と  $\eta_d$  を高くできるが、逆に  $P_{out}$  は小さくなることがわかる。

図3.20 出力電力  $P_{out}$  と効率  $\eta_d$  の  $R_L$  依存特性

$R_L \rightarrow \infty$  ( $\frac{1}{R_L} \rightarrow 0$ ) の時,  $\eta_d$  はB級動作の場合に  $\frac{\pi}{4}$  (78.5%) , A級動作

の場合に  $\frac{1}{2}$  (50%) となるが, 実際にはブレークダウン電圧  $V_{BR}$  を超えて電圧

を印加できないため  $R_L$  は有限の値をとることになる。このため, 上記の理論効

率は得られない。一方,  $R_{on} = 0$  の場合には,  $\eta_d$  は  $R_L$  の値に依存せず常に理論

効率を得ることが出来る。このことは, 高効率化のためにFETデバイスの  $R_{on}$  ができるだけ小さいことが重要であることを意味する<sup>注\*1</sup>。

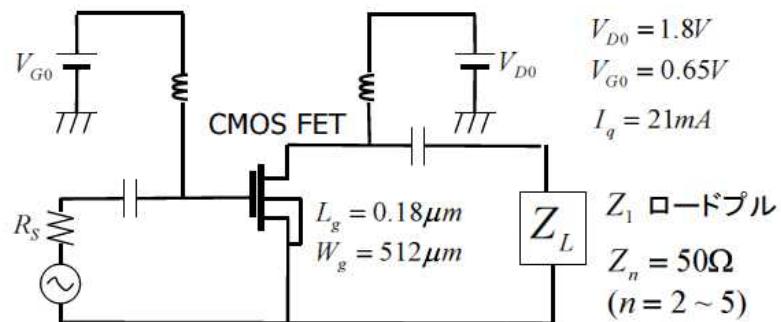

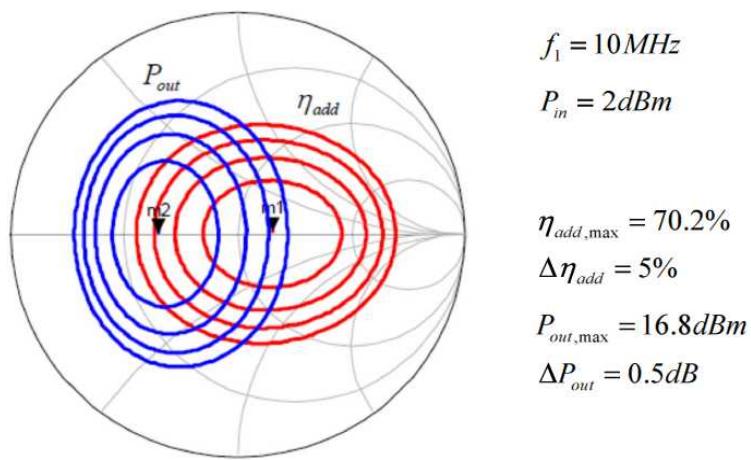

例として, CMOS FET増幅器についてロードプルシミュレーションを行った結果を示す。図3.21にロードプルシミュレーションの回路構成を示す。基本周波数に対する負荷インピーダンス  $Z_1$  を変化 (ロードプル) させ, 増幅器の入出力

特性を計算し, 出力電力  $P_{out}$ , ドレイン効率  $\eta_d$ , 電力付加効率  $\eta_{add}$  特性を求め

ている。ただし, 高調波周波数に対しては  $Z_n = 50\Omega$  ( $n = 2 \sim 5$ ) としている。

注\*1 半導体理論によれば, MOS FETの場合,  $R_{on}$  を小さくするには, ゲート幅  $W_g$  の増大, (単位面積当たり) 酸化膜容量  $C_{ox}$  の増大, ゲート長  $L_g$  の短縮がある。FET増幅器の設計において, 効率を最大化するため, 出力電力から考えると一回り大きめのゲート幅のFETがしばしば用いられる。

図3.21 ロードプルシミュレーションの回路構成 (CMOS FET増幅器の場合)

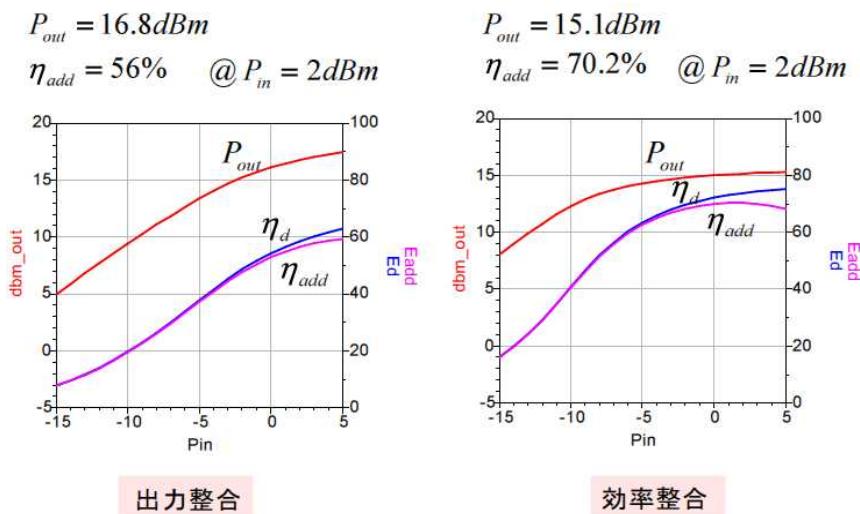

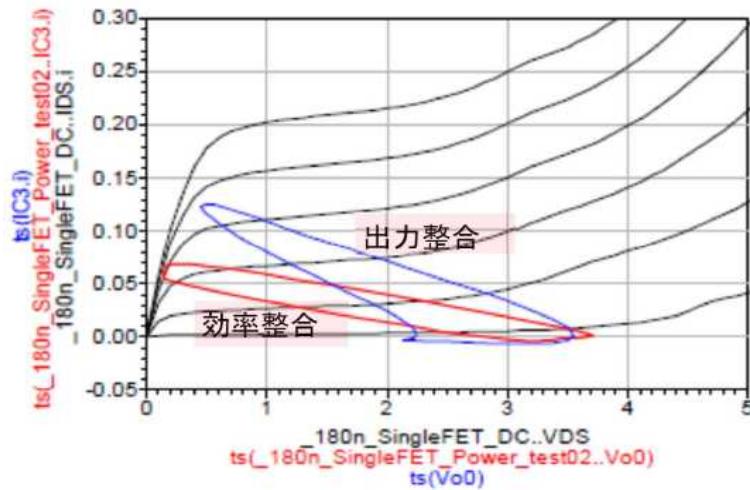

図3.22に周波数10MHzの場合のロードプルシミュレーション結果を示す。

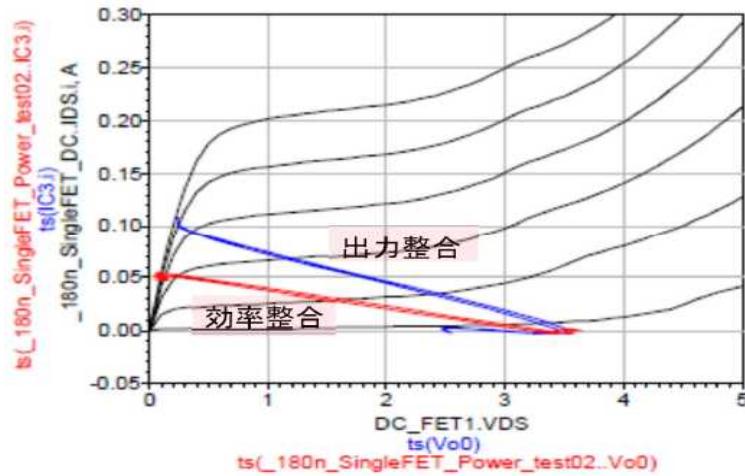

図の(a)はスミスチャート上に示した  $P_{out}$ ,  $\eta_{add}$  に対する等高線図（コンターマップ），(b)は出力整合負荷および効率整合負荷にした場合の入出力特性，(c)は静特性の図に示した出力整合負荷および効率整合負荷にした場合の負荷線（出力端子電圧と電流特性）である。図の(a)および(c)から、効率整合の負荷インピーダンスが出力整合の負荷インピーダンスに比べて大きな値となってい る ( $R_L$  が大きい) ことが確認される。

(a) 等高線図（コンターマップ）

(b) 出力整合および効率整合の場合の入出力特性

(c) 負荷線（出力端子電圧・電流特性）

図3.22 ロードプルシミュレーション結果（10MHz の場合）

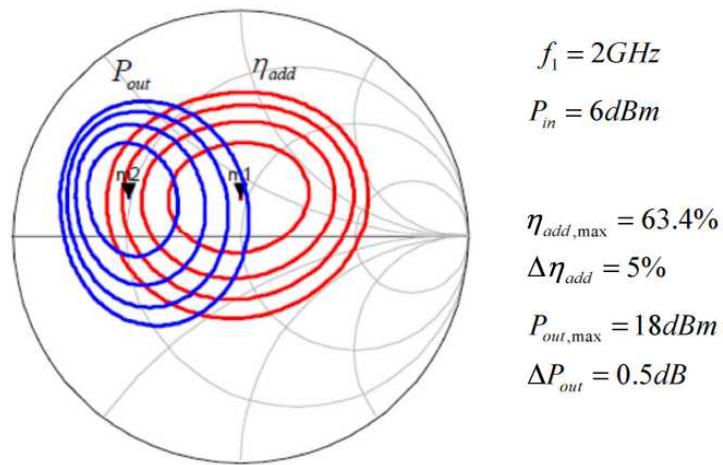

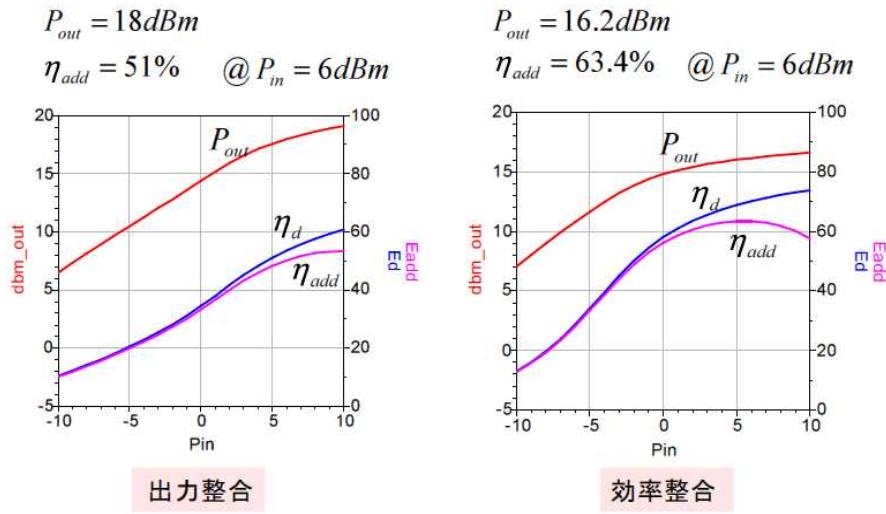

図3.23に周波数 2GHz の場合のロードプルシミュレーション結果を示す。図の(a), (b), (c)は図3.22の場合のそれらに対応している。周波数 2GHz の場合にはFETのサセプタンス成分の影響で負荷線（出力端子電圧と電流特性）が直線とはならないが、出力整合負荷と効率整合負荷のインピーダンスの大小関係の傾向は周波数 10MHz の場合と同様となっている。

(a) 等高線図（コンターマップ）

(b) 出力整合および効率整合の場合の入出力特性

(c) 負荷線（出力端子電圧・電流特性）

図3.23 ロードプルシミュレーション結果（2GHzの場合）

### 3.2.2 ゲートバイアス電圧による高効率動作 (A→B→C 級)

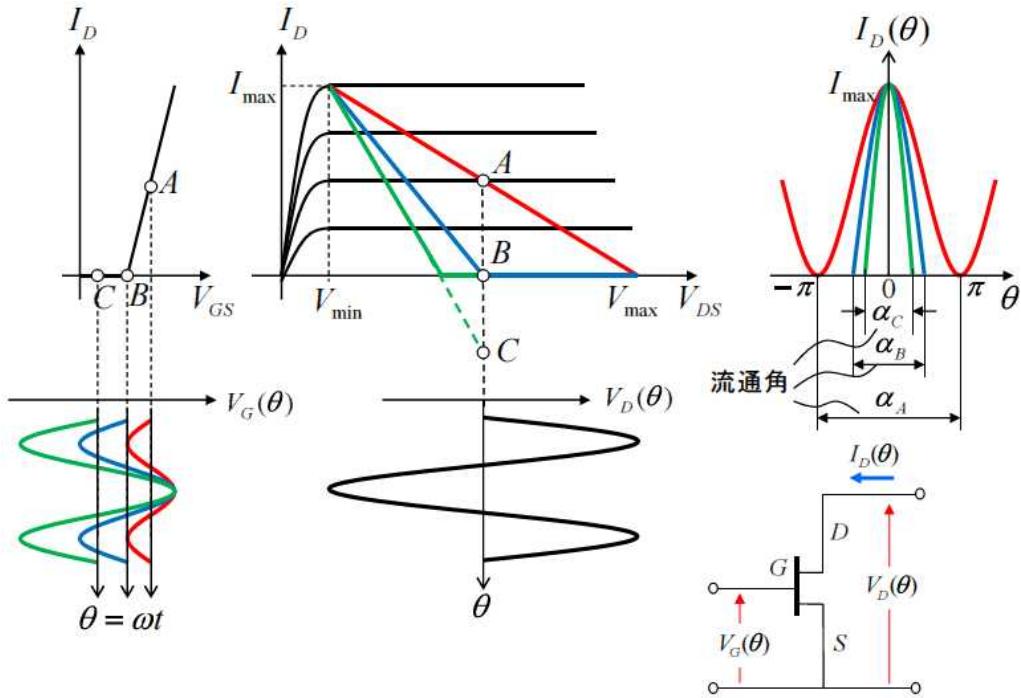

図3.24は、FETの静特性とA, B, C級動作時のバイアス点A, B, C, 端子電圧 $V_G(\theta)$ ,  $V_D(\theta)$ , 電流 $I_D(\theta)$ の波形を示す。1周期を $-\pi \leq \theta \leq \pi$ として, 電

流  $I_D(\theta)$  は  $-\frac{\alpha}{2} \leq \theta \leq \frac{\alpha}{2}$ において流れ、他は流れない。電流  $I_D(\theta)$  が流れる角度  $\alpha$  は流通角と呼ばれ、A級動作では  $\alpha_A = 2\pi$ 、B級動作では  $\alpha_B = \pi$ 、C級動作では  $0 \leq \alpha_C < \pi$  である。

図3.24 FETの静特性とA, B, C級のバイアス点、電流電圧波形、流通角

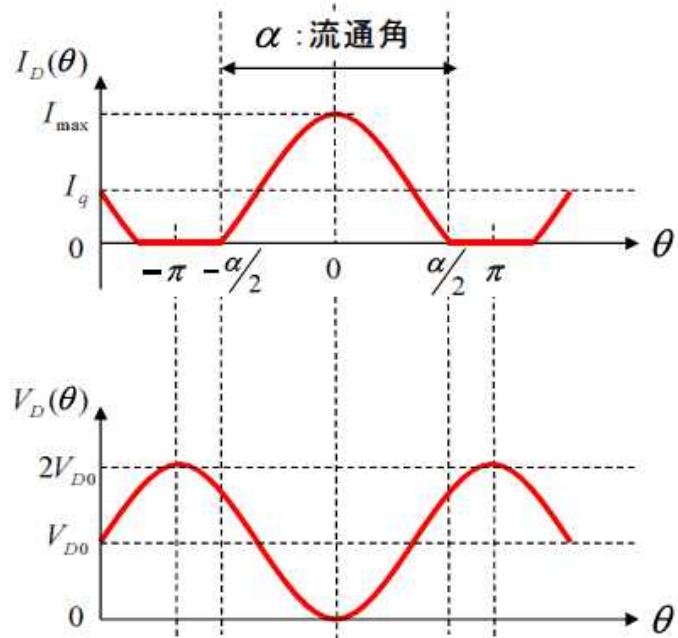

図3.25に、任意の流通角  $\alpha$  における電流  $I_D(\theta)$  と電圧  $V_D(\theta)$  の様子を示す。

ここで、電流  $I_D(\theta)$  は、 $-\pi \leq \theta \leq \pi$  (1周期)において以下で与えられる。

$$\left. \begin{aligned} I_D(\theta) &= I_{\max} \frac{\cos \theta - \cos(\alpha/2)}{1 - \cos(\alpha/2)} & \left( -\frac{\alpha}{2} \leq \theta \leq \frac{\alpha}{2} \right) \\ I_D(\theta) &= 0 & (\text{other}) \end{aligned} \right\} \quad (3.16)$$

上式(3.16)をフーリエ級数展開して次式が得られる。

$$I_D(\theta) = \frac{I_{\max}}{2\pi} \frac{2\sin(\alpha/2) - \alpha \cos(\alpha/2)}{1 - \cos(\alpha/2)} + \frac{I_{\max}}{2\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \cos \theta + \dots \quad (3.17)$$

一方、電圧  $V_D(\theta)$  は以下で与えられる。

$$V_D(\theta) = V_{D0} - V_{D0} \cos \theta \quad (3.18)$$

ここで、 $V_{\min} \approx 0$  と近似している。

図3.25 任意の流通角  $\alpha$  を有する電流  $I_D(\theta)$  と電圧  $V_D(\theta)$  の様子

式(3.17), (3.18)から、直流入力電力  $P_{DC}$ , 基本波出力電力  $P_{out}$ , ドレイイン効率  $\eta_d$ , 基本波負荷  $Z_1$  は次式で与えられる。

$$P_{DC} = \frac{V_{D0} I_{\max}}{2\pi} \frac{2\sin(\alpha/2) - \alpha \cos(\alpha/2)}{1 - \cos(\alpha/2)} \quad (3.19)$$

$$P_{out} = \frac{V_{D0} I_{\max}}{4\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \quad (3.20)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = \frac{\alpha - \sin \alpha}{2(2\sin(\alpha/2) - \alpha \cos(\alpha/2))} \quad (3.21)$$

$$Z_1 = \frac{V_{D0}}{I_{\max}} \frac{2\pi(1 - \cos(\alpha/2))}{(\alpha - \sin \alpha)} \quad (3.22)$$

例えば、B級動作 ( $\alpha = \pi$ ) 時の  $P_{DC}$ ,  $P_{out}$ ,  $\eta_d$ ,  $Z_1$  は以下となる。

$$P_{DC} = \frac{V_{D0} I_{\max}}{\pi}$$

$$P_{out} = \frac{V_{D0} I_{\max}}{4}$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = \frac{\pi}{4} \quad (78.5\%)$$

$$Z_1 = \frac{2V_{D0}}{I_{\max}}$$

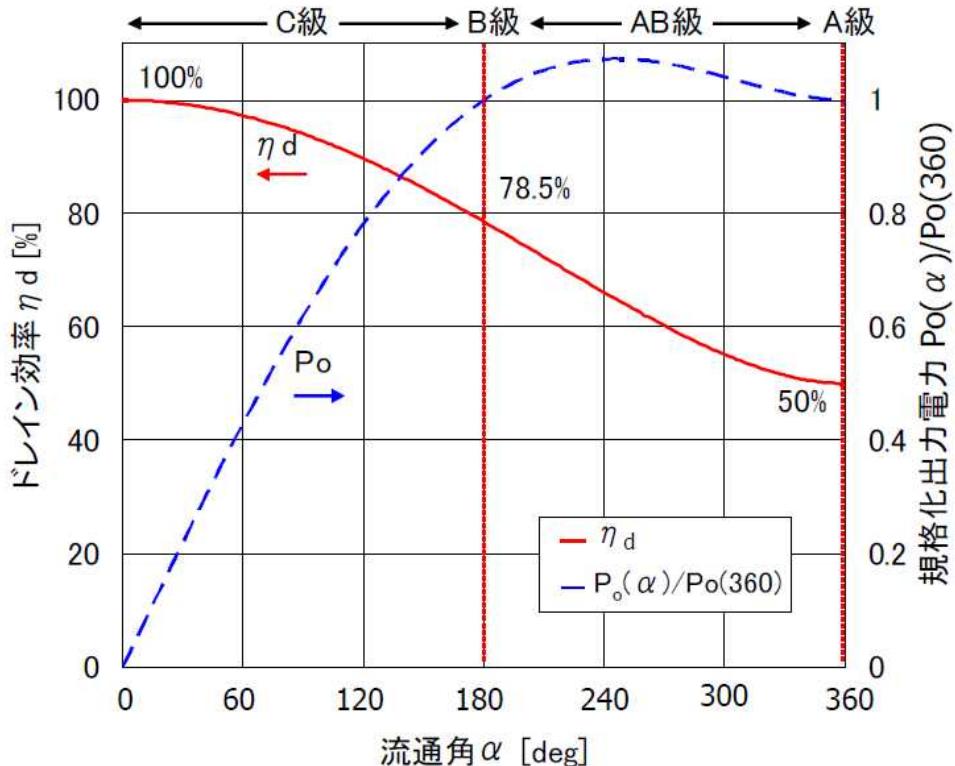

図3.26に流通角  $\alpha$  と出力電力  $P_{out}$ , ドレイイン効率  $\eta_d$  の関係を示す。C級動作で

効率100%が得られるのは  $P_{out} \rightarrow 0$  の極限の場合であることがわかる。

図3.26 A, B, C級動作の流通角  $\alpha$  と出力電力, 効率

### 3.2.3 高調波処理による高効率動作 (F, 逆 F ( $F^{-1}$ ), E 級)

C級動作の場合, 流通角  $\alpha \rightarrow 0$  となる極限で, 理論効率  $\eta_d = 100\%$  が得られるが, その際, 出力電力は  $P_{out} = 0$  となってしまう問題がある。これに対し, A級もしくはB級と同等の出力電力  $P_{out}$  を得つつ, 効率  $\eta_d = 100\%$  が得られる高効率回路方式として, 後述のF級動作<sup>[3]</sup>, 逆F( $F^{-1}$ )級動作<sup>[4]</sup>, E級動作<sup>[5]</sup>がある。これらは, FETの端子電流  $I_D(\theta)$ , 電圧  $V_D(\theta)$ の波形を適切に成形し, FET内で消費される電力を  $P_C \rightarrow 0$  とすることにより実現される。このような電流,

電圧波形は、B級動作のゲートバイアス電圧を印加するとともに、適切な高調波処理を行うことにより得られる。

### (1) F級増幅器

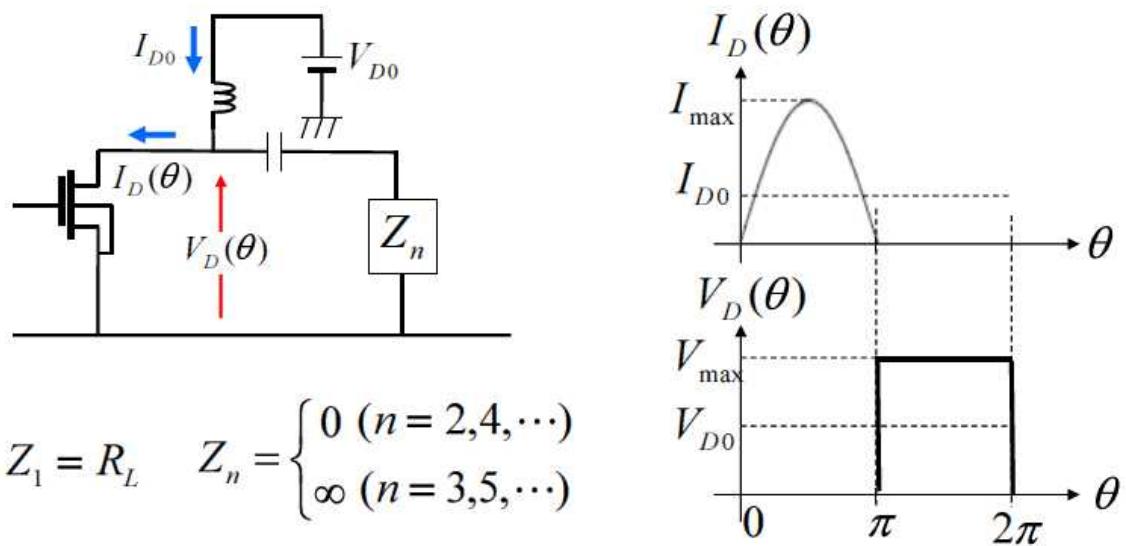

図3.27にF級増幅器の回路構成と端子電流 $I_D(\theta)$ 、電圧 $V_D(\theta)$ の波形を示す。

なおここでは、見通し良い解析を行うため、ニード電圧 $V_k = 0$ （オン抵抗 $R_{on} = 0$ ）と近似している。

図3.27 F級増幅器の出力回路構成と電流電圧波形

F級動作ではB級動作のゲートバイアス電圧を印加するとともに、適切な高調波処理を行うことにより、 $I_D(\theta)$ を半波整流波形に成形し、 $V_D(\theta)$ を矩形に成形する。これによりFETで消費される電力が $P_C \rightarrow 0$ となり、効率 $\eta_d = 100\%$ が得られる。以下で、F級動作について定量解析する。

図の電流 $I_D(\theta)$ 、電圧 $V_D(\theta)$ は以下で与えられる。

$$I_D(\theta) = \begin{cases} I_{\max} \sin \theta & (0 \leq \theta < \pi) \\ 0 & (\pi \leq \theta < 2\pi) \end{cases} \quad (3.23)$$

$$V_D(\theta) = \begin{cases} 0 & (0 \leq \theta < \pi) \\ V_{\max} & (\pi \leq \theta < 2\pi) \end{cases} \quad (3.24)$$

これをフーリエ級数展開すると、 $I_D(\theta)$ ,  $V_D(\theta)$ は次式で表わせる。

$$\begin{aligned} I_D(\theta) &= \frac{I_{\max}}{\pi} + \frac{I_{\max}}{2} \sin \theta - \frac{2I_{\max}}{\pi} \sum_{n=2,4,\dots} \frac{1}{n^2-1} \cos(n\theta) \\ &= I_{D0} + \frac{\pi I_{D0}}{2} \sin \theta - 2I_{D0} \sum_{n=2,4,\dots} \frac{1}{n^2-1} \cos(n\theta) \end{aligned} \quad (3.25)$$

$$\begin{aligned} V_D(\theta) &= \frac{V_{\max}}{2} - \frac{2V_{\max}}{\pi} \sin \theta - \frac{2V_{\max}}{\pi} \sum_{n=3,5,\dots} \frac{1}{n} \sin(n\theta) \\ &= V_{D0} - \frac{4V_{D0}}{\pi} \sin \theta - \frac{4V_{D0}}{\pi} \sum_{n=3,5,\dots} \frac{1}{n} \sin(n\theta) \end{aligned} \quad (3.26)$$

F級の場合には、 $I_{\max}$ ,  $V_{\max}$ は、バイアス電流  $I_{D0}$ , 電圧  $V_{D0}$ と以下で関係付けられる。

$$I_{D0} = \frac{I_{\max}}{\pi} \quad \rightarrow \quad I_{\max} = \pi I_{D0} \quad (3.27)$$

$$V_{D0} = \frac{V_{\max}}{2} \quad \rightarrow \quad V_{\max} = 2V_{D0} \quad (3.28)$$

式(3.25)から、 $I_D(\theta)$ は直流、基本波、および偶数次高調波成分から成り、

奇数次高調波成分は含まない。一方、式(3.26)から、 $V_D(\theta)$ は直流、基本波、および奇数次高調波成分から成り、偶数次高調波成分は含まない。このような波形を実現するためには、高調波にたいする負荷インピーダンス $Z_n$ を以下とする必要がある。

$$Z_n = \begin{cases} 0 & (\text{short}) \quad (n = 2, 4, \dots) \\ \infty & (\text{open}) \quad (n = 3, 5, \dots) \end{cases} \quad (3.29)$$

式(3.25), (3.26)から、直流電力 $P_{DC}$ 、基本波出力電力 $P_{out}$ 、ドレイイン効率 $\eta_d$ 、基本波に対する負荷インピーダンス $Z_1$ は次式で与えられる。

$$P_{DC} = \frac{I_{\max} V_{\max}}{2\pi} = \frac{I_{\max} V_{D0}}{\pi} = I_{D0} V_{D0} \quad (3.30)$$

$$P_{out} = \frac{I_{\max} V_{\max}}{2\pi} = \frac{I_{\max} V_{D0}}{\pi} = I_{D0} V_{D0} \quad (3.31)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = 1 (100\%) \quad (3.32)$$

$$Z_1 = \frac{4}{\pi} \frac{V_{\max}}{I_{\max}} = \frac{8}{\pi} \frac{V_{D0}}{I_{\max}} = \frac{8}{\pi^2} \frac{V_{D0}}{I_{D0}} \quad (3.33)$$

F級動作は $\eta_d = 100\%$ が得られ、かつ、B級動作に比べて同等以上の $P_{out}$ が得られるといえる ( $\frac{I_{\max} V_{D0}}{4} (B\text{級}) \leq \frac{I_{\max} V_{D0}}{\pi} (F\text{級})$ )。

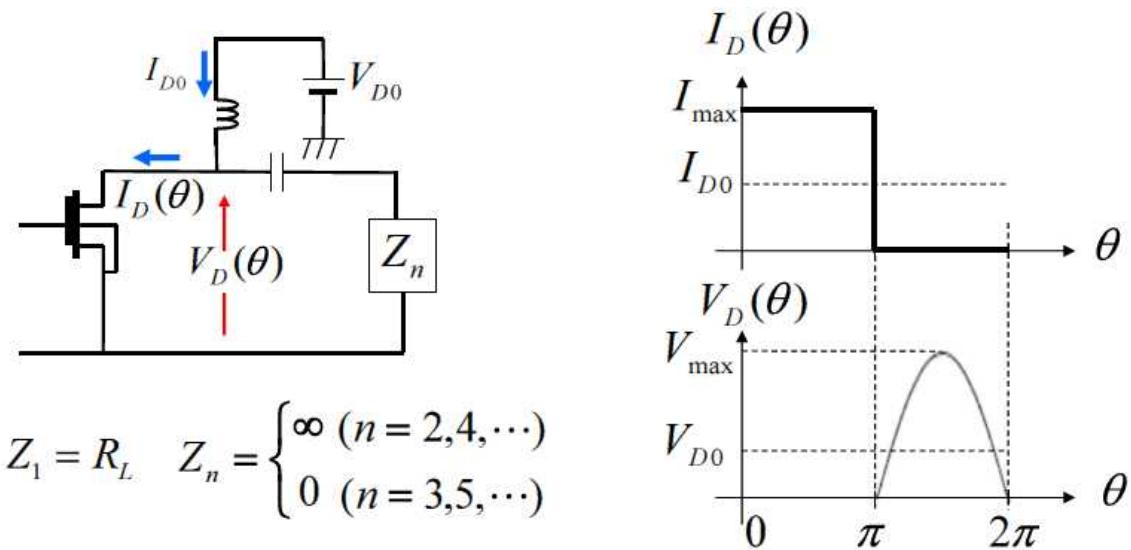

## (2) 逆F(F<sup>-1</sup>)級増幅器

図3.28に逆F(F<sup>-1</sup>)級増幅器の回路構成と端子電流 $I_D(\theta)$ 、電圧 $V_D(\theta)$ の波形を示す。ここでも、ニ一電圧 $V_k = 0$ （オン抵抗 $R_{on} = 0$ ）と近似している。

図3.28 F<sup>-1</sup>級増幅器の出力回路構成と電流電圧波形

F<sup>-1</sup>級動作ではB級動作のゲートバイアス電圧を印加するとともに、適切な高調波処理を行うことにより、 $I_D(\theta)$ を矩形に成形し、 $V_D(\theta)$ を半波整流波形に成形する。これによりFETで消費される電力が $P_C \rightarrow 0$ となり、効率 $\eta_d = 100\%$ が得られる。以下で、F<sup>-1</sup>級動作について定量解析する。

図の電流 $I_D(\theta)$ 、電圧 $V_D(\theta)$ は以下で与えられる。

$$I_D(\theta) = \begin{cases} I_{max} & (0 \leq \theta < \pi) \\ 0 & (\pi \leq \theta < 2\pi) \end{cases} \quad (3.34)$$

$$V_D(\theta) = \begin{cases} 0 & (0 \leq \theta < \pi) \\ -V_{\max} \sin \theta & (\pi \leq \theta < 2\pi) \end{cases} \quad (3.35)$$

これをフーリエ級数展開すると、 $I_D(\theta)$ ,  $V_D(\theta)$ は次式で表わせる。

$$\begin{aligned} I_D(\theta) &= \frac{I_{\max}}{2} + \frac{2I_{\max}}{\pi} \sin \theta + \frac{2I_{\max}}{\pi} \sum_{n=3,5,\dots} \frac{1}{n} \sin(n\theta) \\ &= I_{D0} + \frac{4I_{D0}}{\pi} \sin \theta + \frac{4I_{D0}}{\pi} \sum_{n=3,5,\dots} \frac{1}{n} \sin(n\theta) \end{aligned} \quad (3.36)$$

$$\begin{aligned} V_D(\theta) &= \frac{V_{\max}}{\pi} - \frac{V_{\max}}{2} \sin \theta + \frac{2V_{\max}}{\pi} \sum_{n=2,4,\dots} \frac{1}{n^2-1} \cos(n\theta) \\ &= V_{D0} - \frac{\pi V_{D0}}{2} \sin \theta + 2V_{D0} \sum_{n=2,4,\dots} \frac{1}{n^2-1} \cos(n\theta) \end{aligned} \quad (3.37)$$

F<sup>-1</sup>級の場合には、 $I_{\max}$ ,  $V_{\max}$ は、バイアス電流 $I_{D0}$ , 電圧 $V_{D0}$ と以下で関係付けられる。

$$I_{D0} = \frac{I_{\max}}{2} \quad \rightarrow \quad I_{\max} = 2I_{D0} \quad (3.38)$$

$$V_{D0} = \frac{V_{\max}}{\pi} \quad \rightarrow \quad V_{\max} = \pi V_{D0} \quad (3.39)$$

式(3.36)から、 $I_D(\theta)$ は直流、基本波、および奇数次高調波成分から成り、偶数次高調波成分は含まない。一方、式(3.37)から、 $V_D(\theta)$ は直流、基本波、および偶数次高調波成分から成り、奇数次高調波成分は含まない。このような

波形を実現するためには、高調波にたいする負荷インピーダンス  $Z_n$  を以下とする必要がある。

$$Z_n = \begin{cases} \infty & (\text{open}) \quad (n = 2, 4, \dots) \\ 0 & (\text{short}) \quad (n = 3, 5, \dots) \end{cases} \quad (3.40)$$

式(3.36), (3.37)から、直流電力  $P_{DC}$ , 基本波出力電力  $P_{out}$ , ドレイイン効率  $\eta_d$ ,

基本波に対する負荷インピーダンス  $Z_1$  は次式で与えられる。

$$P_{DC} = \frac{I_{\max} V_{\max}}{2\pi} = \frac{I_{\max} V_{D0}}{2} = I_{D0} V_{D0} \quad (3.41)$$

$$P_{out} = \frac{I_{\max} V_{\max}}{2\pi} = \frac{I_{\max} V_{D0}}{2} = I_{D0} V_{D0} \quad (3.42)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = 1 (100\%) \quad (3.43)$$

$$Z_1 = \frac{\pi}{4} \frac{V_{\max}}{I_{\max}} = \frac{\pi^2}{4} \frac{V_{D0}}{I_{\max}} = \frac{\pi^2}{8} \frac{V_{D0}}{I_{D0}} \quad (3.44)$$

$F^{-1}$ 級動作は  $\eta_d = 100\%$  が得られ、かつ、B級動作に比べて同等以上の  $P_{out}$  が得

られるといえる ( $\frac{I_{\max} V_{D0}}{4} (B\text{級}) \leq \frac{I_{\max} V_{D0}}{2} (F^{-1}\text{級})$ )。

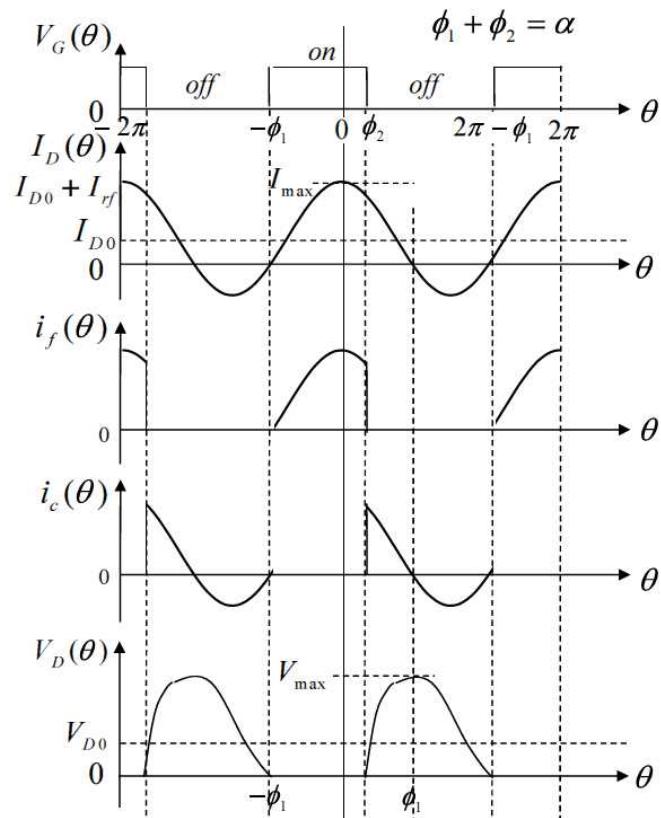

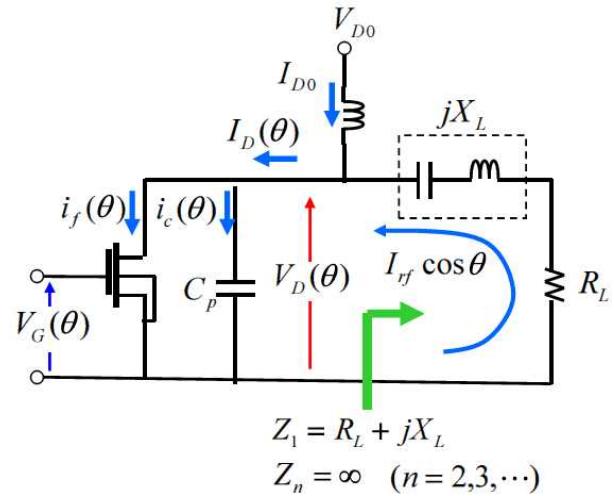

### (3) E級増幅器

図3.29にE級増幅器の出力回路構成と電流、電圧波形を示す。FETは理想スイ

ツチとして動作するとしている。FETの出力側に並列に容量  $C_p$  が接続され、負荷はすべての高調波に対してオープン（電流が流れない）、基本波に対して  $Z_1 = R_L + jX_L$  となっている。

図3.29 E級増幅器の出力回路構成と電流、電圧波形

出力側電流  $I_D(\theta)$  は直流バイアス電流  $I_{D0}$  と負荷を流れるRF（基本波）電流

$I_{rf} \cos \theta$  でなり，次式で与えられる。ここで， $\theta = \omega t$  ( $\omega$  は基本波角周波数)。

$$I_D(\theta) = I_{D0} + I_{rf} \cos \theta = I_{D0}(1 + m \cos \theta) \quad (3.45)$$

$$\text{ここで, } m = \frac{I_{rf}}{I_{D0}} \quad (3.46)$$

さらに，1周期  $(-\phi_1 \leq \theta \leq 2\pi - \phi_1)$ において， $I_D(\theta)$  はFETを流れる電流  $i_f(\theta)$  と容量  $C_P$  を流れる電流  $i_c(\theta)$  を用いて以下のように表わせる。

$$I_D(\theta) = \begin{cases} i_f(\theta) & (-\phi_1 \leq \theta \leq \phi_2) \\ i_c(\theta) & (\phi_2 \leq \theta \leq 2\pi - \phi_1) \end{cases} \quad (3.47)$$

ここで以下の前提条件を与える。

$$I_D(\theta = -\phi_1) = 0 \quad ; \text{ FETが } on \text{ を開始する位相 } -\phi_1 \text{ で電流が } 0$$

$$\int_{\phi_2}^{2\pi - \phi_1} I_D(\theta) d\theta = 0 \quad ; \text{ FETが } off \text{ 時に容量 } C_P \text{ に流入する電荷総量は } 0$$

これから， $m$  に関して次式が得られる。

$$m = \frac{-1}{\cos(\phi_1)} \quad (3.48)$$

$$m^2 = 1 + \left( \frac{2\pi + \sin \alpha - \alpha}{1 - \cos \alpha} \right)^2 \quad (3.49)$$

ここで、 $\alpha = \phi_1 + \phi_2$  (流通角)

この時、FETに印加される電圧  $V_D(\theta)$  は以下となる。

$$V_D(\theta) = \begin{cases} 0 & (-\phi_1 \leq \theta \leq \phi_2) \\ \frac{I_{D0}}{\omega C_p} (\theta + m \sin \theta - \phi_2 - m \sin \phi_2) & (\phi_2 \leq \theta \leq 2\pi - \phi_1) \end{cases} \quad (3.50)$$

上式(3.50)の2行目式は以下から得られる。

$$V_D(\theta) = \frac{1}{\omega C_p} \int_{\phi_2}^{\theta} i_C(\theta) d\theta = \frac{1}{\omega C_p} \int_{\phi_2}^{\theta} I_D(\theta) d\theta \quad (3.51)$$

ここで、 $V_D(\theta = 2\pi - \phi_1) = 0$  から、以下が成り立つ必要がある。

$$2\pi - \alpha = m(\sin \phi_1 + \sin \phi_2) \quad (3.52)$$

図3.29から、FETに電流  $i_f(\theta)$  が流れている時には電圧は0となっており、FETに0でない電圧  $V_D(\theta)$  がかかっている時には電流は0となっている。これから、FET内部で消費される電力は  $P_C = 0$  となり、ドレイン効率が  $\eta_d = 1$  (100%) となる。

以下、詳細に解析する。まず、 $V_D(\theta)$  を以下のように表わす。

$$V_D(\theta) = V_{D0} + V_{ci} \cos \theta + V_{cq} \sin \theta \quad (3.53)$$

式 (3.50) および (3.52) を用いて、式 (3.53) の  $V_{D0}$ ,  $V_{ci}$ ,  $V_{cq}$  は以下のように求まる。

$$\begin{aligned} V_{D0} &= \frac{1}{2\pi} \int_{2\pi} V_D(\theta) d\theta = \frac{1}{2\pi} \int_{\phi_2}^{2\pi-\phi_1} V_D(\theta) d\theta \\ &= \frac{I_{D0}m}{4\pi\omega C_p} \left( m(\sin^2 \phi_1 - \sin^2 \phi_2) + 2(\cos \phi_2 - \cos \phi_1) \right) \end{aligned} \quad (3.54)$$

$$\begin{aligned} V_{ci} &= \frac{1}{\pi} \int_{2\pi} V_D(\theta) \cos(\theta) d\theta = \frac{1}{\pi} \int_{\phi_2}^{2\pi-\phi_1} V_D(\theta) \cos(\theta) d\theta \\ &= -\frac{I_{D0}}{2\pi\omega C_p} \left( m(\sin^2 \phi_1 - \sin^2 \phi_2) + 2(\cos \phi_2 - \cos \phi_1) \right) = -\frac{2}{m} V_{D0} \end{aligned} \quad (3.55)$$

$$\begin{aligned} V_{cq} &= \frac{1}{\pi} \int_{2\pi} V_D(\theta) \sin(\theta) d\theta = \frac{1}{\pi} \int_{\phi_2}^{2\pi-\phi_1} V_D(\theta) \sin(\theta) d\theta \\ &= \frac{mI_{D0}}{2\pi\omega C_p} \left( \left( m - \frac{2}{m} \right) (\sin \phi_1 + \sin \phi_2) - \frac{1}{2} (\sin 2\phi_1 + \sin 2\phi_2) \right) \end{aligned} \quad (3.56)$$

これから、

$$\begin{aligned} P_{out} &= -\frac{1}{2} I_{rf} V_{ci} = -\frac{1}{2} (mI_{D0}) \left( -\frac{2}{m} V_{D0} \right) = I_{D0} V_{D0} = P_{DC} \\ &= \frac{4\pi\omega C_p {V_{D0}}^2}{m \left( m(\sin^2 \phi_1 - \sin^2 \phi_2) + 2(\cos \phi_2 - \cos \phi_1) \right)} \end{aligned} \quad (3.57)$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = 1 \quad (100\%) \quad (3.58)$$

また、基本波に対する負荷インピーダンス  $Z_1 = R_L + jX_L$  は以下で与えられる

(付録C参照)。

$$R_L = -\frac{V_{ci}}{I_{rf}} = \frac{1}{2\pi\omega C_p m} (m(\sin^2 \phi_1 - \sin^2 \phi_2) + 2(\cos \phi_2 - \cos \phi_1)) \quad (3.59)$$

$$X_L = \frac{V_{cq}}{I_{rf}} = \frac{1}{2\pi\omega C_p} \left( (m - \frac{2}{m})(\sin \phi_1 + \sin \phi_2) - \frac{1}{2}(\sin 2\phi_1 + \sin 2\phi_2) \right) \quad (3.60)$$

以下では特に、B級のゲートバイアス印加時について検討する。B級ゲートバイアス印加時には  $\alpha = \phi_1 + \phi_2 = \pi$  であり、式(3.49)から  $m = 1.862$  となる。さらに、式(3.48)から  $\phi_1 = 122.5^\circ$ ,  $\phi_2 = 57.5^\circ$  となる。上記  $m$ ,  $\phi_1$ ,  $\phi_2$  を用いると、以下が得られる。

$$V_{D0} = \frac{I_{D0}}{\pi\omega C_p} \quad (5.54),$$

$$V_{ci} = -1.074 \frac{I_{D0}}{\pi\omega C_p} = -1.074 V_{D0} \quad (3.55),$$

$$V_{cq} = 1.237 \frac{I_{D0}}{\pi\omega C_p} = 1.237 V_{D0} \quad (3.56),$$

$$P_{out} = -\frac{1}{2} I_{rf} V_{ci} = -\frac{1}{2} (m I_{D0}) \left( -\frac{2}{m} V_{D0} \right) = I_{D0} V_{D0} = P_{DC} = \pi\omega C_p V_{D0}^2 \quad (3.57),$$

$$\eta_d = \frac{P_{out}}{P_{DC}} = 1 \quad (100\%) \quad (5.58),$$

ここで、直流電流  $I_{D0}$  はFETに流れる最大電流  $I_{\max}$  と以下で関係付けられる。

$$I_{\max} = I_{D0} + I_{rf} = I_{D0}(1+m) \quad \rightarrow \quad I_{D0} = \frac{I_{\max}}{1+m} \quad (3.61)$$

上式(3.61), (3.54)', およびB級バイアス時の  $m = 1.862$  を用いて  $C_p$  は以下で与えられる。

$$C_p = \frac{I_{D0}}{\pi\omega V_{D0}} = \frac{I_{\max}}{\pi\omega V_{D0}} \frac{1}{1+m} = \frac{I_{\max}}{2.862\pi\omega V_{D0}} \quad (3.62)$$

$C_p$  として上式(3.62)を用いると  $P_{out}$  は以下となる。

$$P_{out} = \pi\omega C_p V_{D0}^2 = \frac{V_{D0} I_{\max}}{2.862} \quad (3.57)''$$

また、基本波に対する負荷インピーダンス  $Z_1 = R_L + jX_L$  は以下となる。

$$Z_1 = (1.074 + j1.237) \frac{V_{D0}}{I_{rf}} = (1.65 + j1.9) \frac{V_{D0}}{I_{\max}} = 1.91 e^{j0.27\pi} \frac{V_{D0}}{I_{\max}} \quad (3.63)$$

上式(3.57)', (および(3.57) '') によれば、 $C_p$  の値が大きいほど  $P_{out}$  も大きくなる。それでは、 $C_p$  は大きい程よいのであろうか？ 式(3.62)によれば  $C_p$  の増大により  $I_{\max}$  が増大することになる。すると、負荷線が効率整合から出力整

合に近づくことになる（図3.22(c)参照）。実際のFETでは $R_{on} \neq 0$ であり、この場合、効率が低下することになる（3.2.1節参照）。このため、 $C_p$ の値は出力特性と効率特性のトレードオフにより決める必要があるといえる（後述の図3.33参照）。

次に、バイアス電流 $I_{D0}$ 、電圧 $V_{D0}$ と最大電流 $I_{\max}$ 、電圧 $V_{\max}$ の関係を求めること。式(3.61)から、以下で与えられる。

$$\frac{I_{\max}}{I_{D0}} = 1 + m = 2.862 \quad (3.64)$$

$V_{\max}$ は式(3.50)において、 $\theta = \phi_1$ の時の $V_D(\theta)$ として与えられ以下となる（図3.29参照）。

$$\begin{aligned} V_{\max} &= V_D(\theta = \phi_1) = \frac{I_{D0}}{\omega C_p} (\phi_1 + m \sin \phi_1 - \phi_2 - m \sin \phi_2) \\ &= 0.362\pi \frac{I_{D0}}{\omega C_p} \end{aligned} \quad (3.65)$$

$V_{D0}$ に対する式(3.54)' と上式(3.65)から、以下が得られる。

$$\frac{V_{\max}}{V_{D0}} = 0.362\pi^2 \quad (3.66)$$

これまでに得られたB、F、逆F( $F^{-1}$ )、E級動作の理論式を表3.1にまとめた。表は、同一のドレインバイアス電圧 $V_{D0}$ を印加し、また、FETのオン抵抗が

$R_{on} = 0$  と近似した場合のものである。同一の  $V_{D0}$  の場合、 $P_{out}$  は、B級<F級<E級<F<sup>-1</sup>級の順で大きくなっている。これは、RF（基本波）の電流および電圧の振

れ幅が大きくなるためである。一方、 $\frac{V_{\max}}{V_{D0}}$  は、B級=F級<F<sup>-1</sup>級<E級の順で大き

くなっている。この順でブレークダウン電圧  $V_{BR}$  への電圧の振り込みが生じやすくなることに留意する必要がある。

表3.1 B, F, 逆F (F<sup>-1</sup>), E級動作の理論式まとめ

近似:  $R_{on} \approx 0$

|                           | B級                         | F級                                      | F <sup>-1</sup> 級                         | E級                                         |

|---------------------------|----------------------------|-----------------------------------------|-------------------------------------------|--------------------------------------------|

| $P_{out}$                 | $\frac{V_{D0}I_{\max}}{4}$ | $\frac{V_{D0}I_{\max}}{\pi}$            | $\frac{V_{D0}I_{\max}}{2}$                | $\frac{V_{D0}I_{\max}}{2.862}$             |

| $\eta_d$                  | $\frac{\pi}{4}$            | 1                                       | 1                                         | 1                                          |

| $Z_1$                     | $\frac{2V_{D0}}{I_{\max}}$ | $\frac{8}{\pi} \frac{V_{D0}}{I_{\max}}$ | $\frac{\pi^2}{4} \frac{V_{D0}}{I_{\max}}$ | $1.91e^{j0.27\pi} \frac{V_{D0}}{I_{\max}}$ |

| $Z_n$                     | 0                          | 0 (n:even)<br>$\infty$ (n:odd)          | $\infty$ (n:even)<br>0 (n:odd)            | $\infty$                                   |

| $\frac{I_{\max}}{I_{D0}}$ | $\pi$                      | $\pi$                                   | 2                                         | 2.862                                      |

| $\frac{V_{\max}}{V_{D0}}$ | 2                          | 2                                       | $\pi$                                     | $0.362\pi^2$<br>(3.57)                     |

#### (4) シミュレーション検討

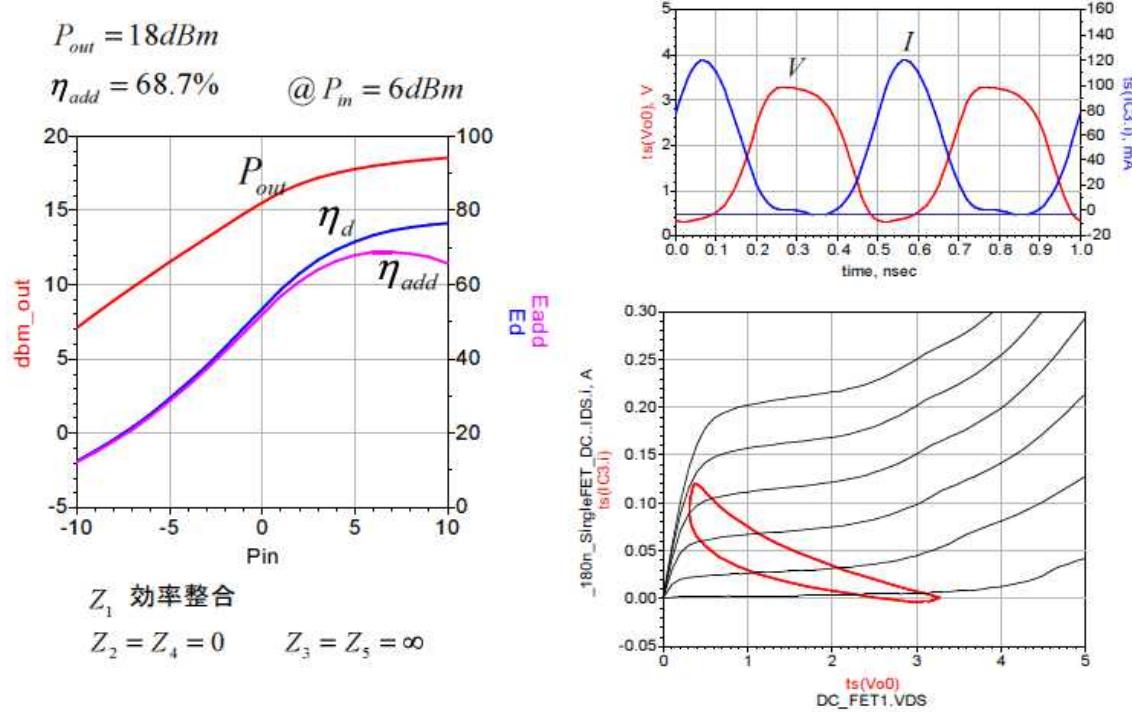

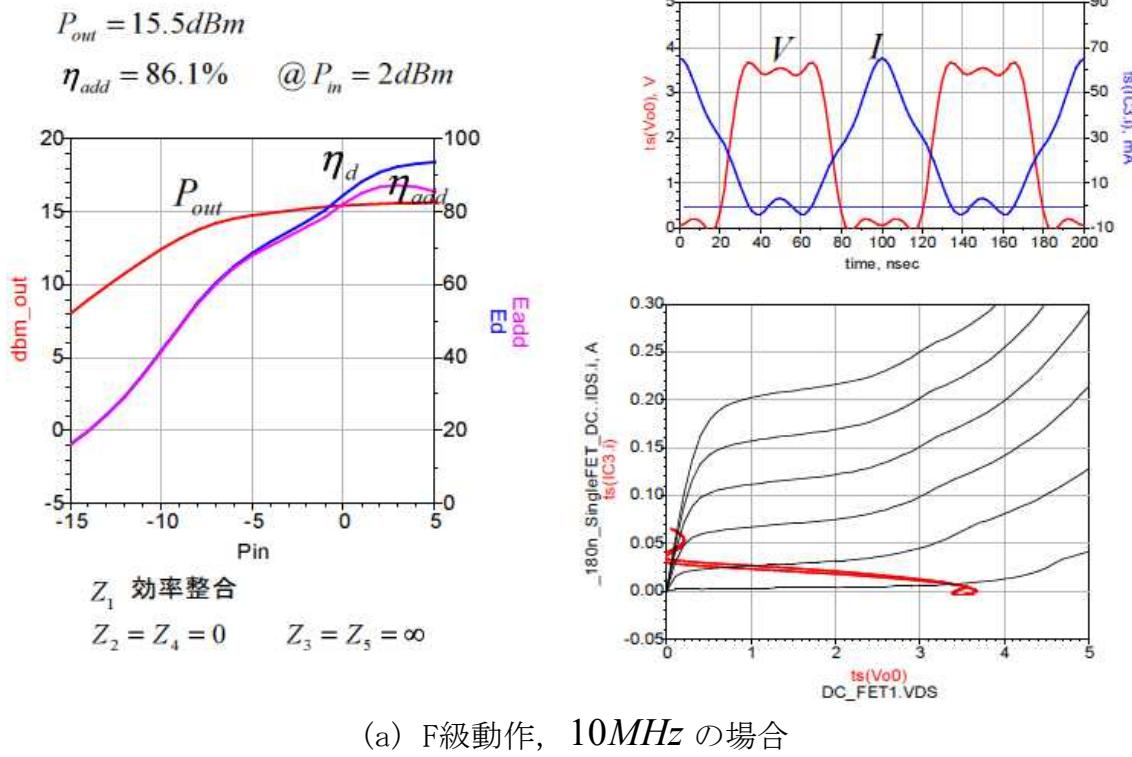

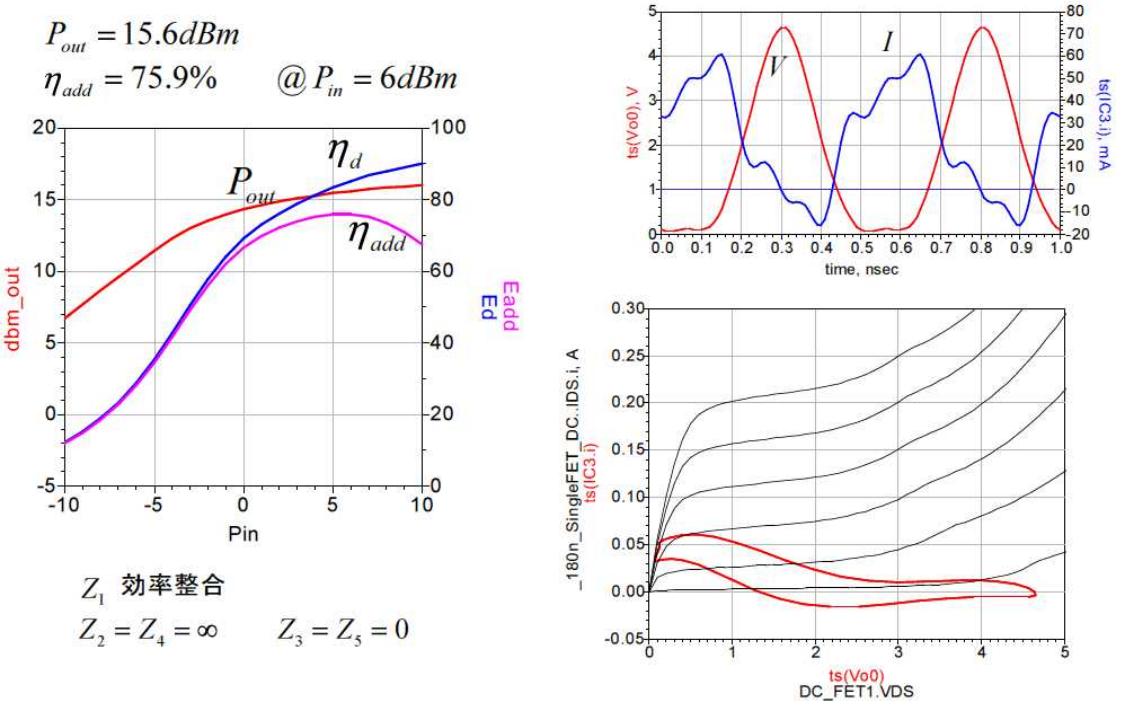

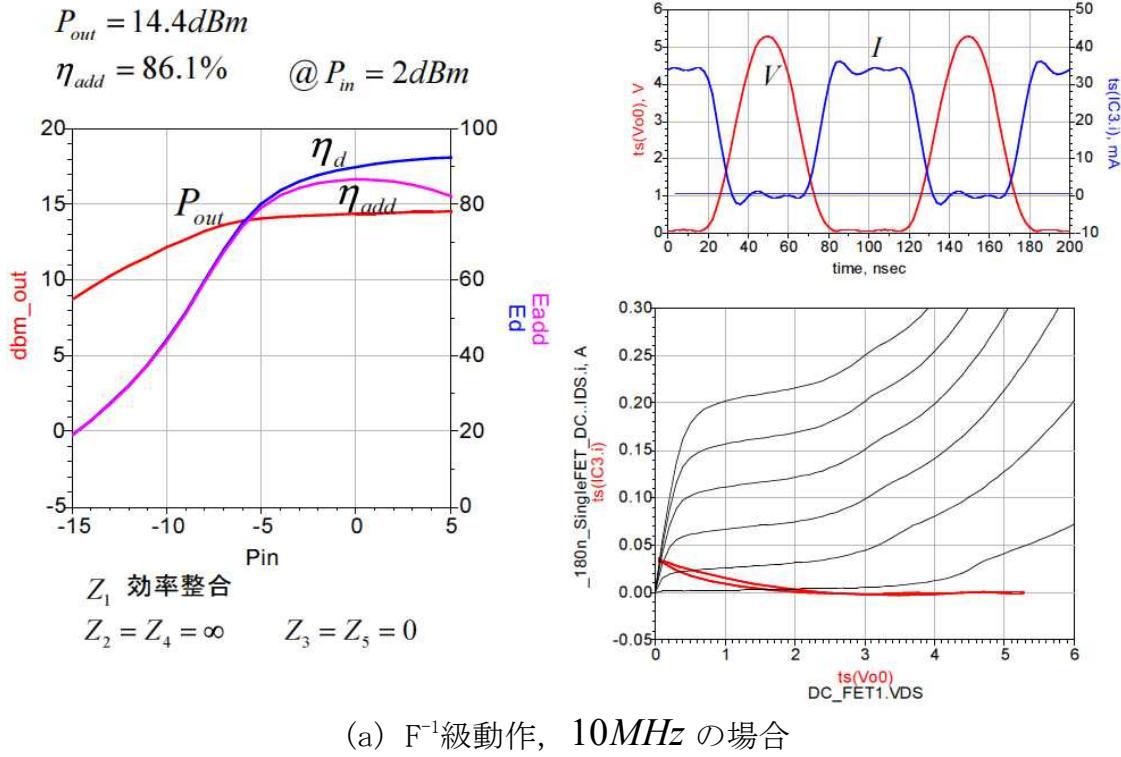

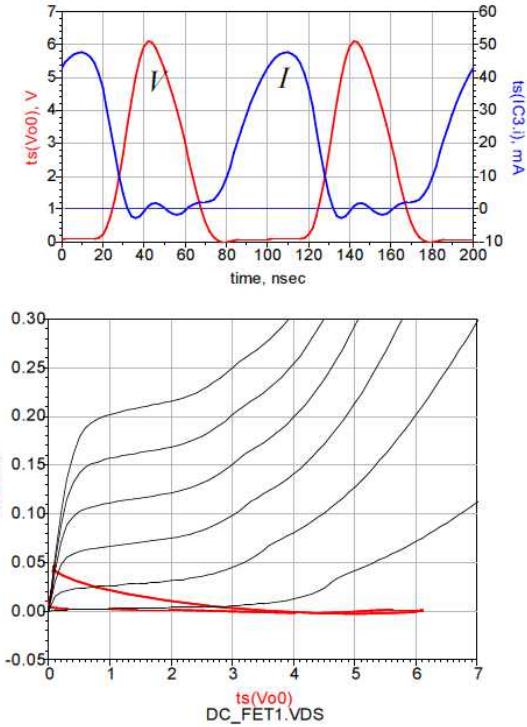

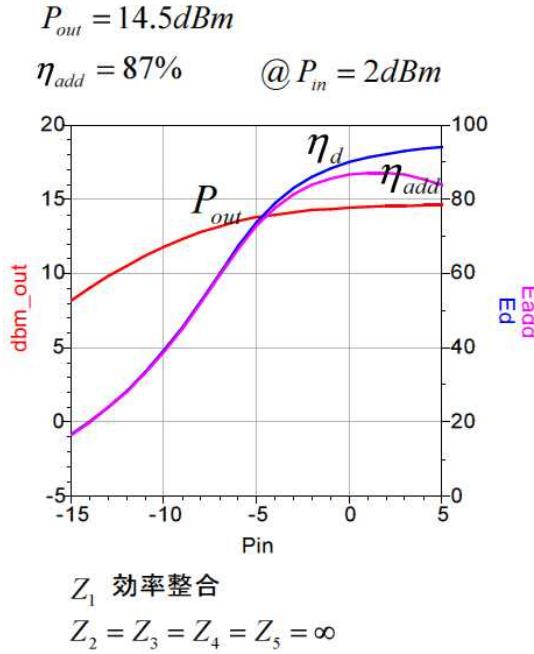

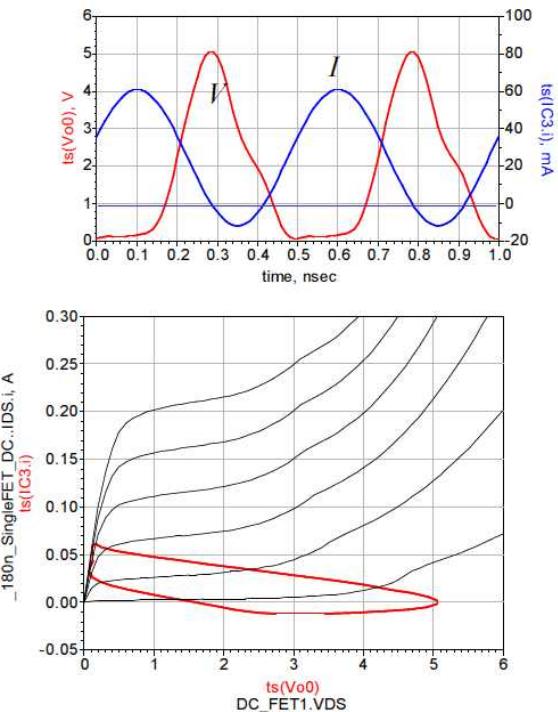

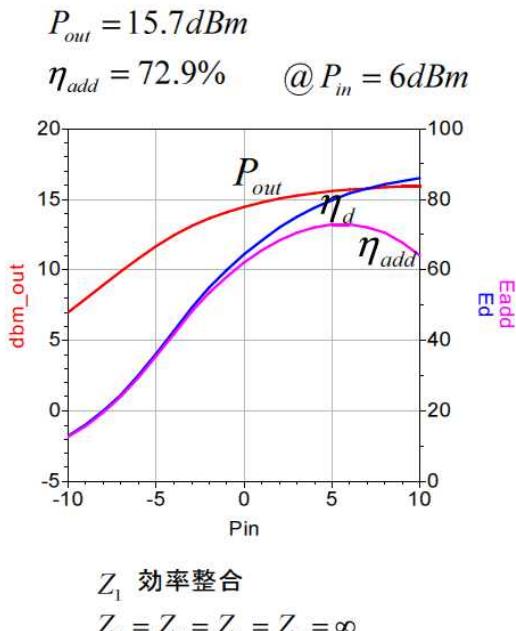

CMOS FET (ゲート長  $L_g = 0.18\mu m$ , ゲート幅  $W_g = 512\mu m$ ) を用いた高効率動作級 (F, F<sup>-1</sup>, E級) 増幅器のシミュレーション検討結果について述べる。シミュレーションは、B級バイアス ( $V_{D0} = 1.8V$ ,  $V_{G0} = 0.65V$ ) を印加し、(a) FET の寄生サセプタンスの影響を無視できる (基本) 周波数  $10MHz$ , および、(b) FET の寄生サセプタンスの影響が無視できなくなる (基本) 周波数  $2GHz$  で行った。

図3.30 (a), (b)にF級動作のシミュレーション結果を、図3.31(a), (b)にF<sup>-1</sup>級動作のシミュレーション結果を、また、図3.32(a), (b)にE級動作のシミュレーション結果を示す。各図の(a)は10MHzの場合、(b)は2GHzの場合である。各図には、効率整合負荷での入出力特性、電流、電圧波形、および負荷線特性（出力端子電圧と電流特性）を示している。

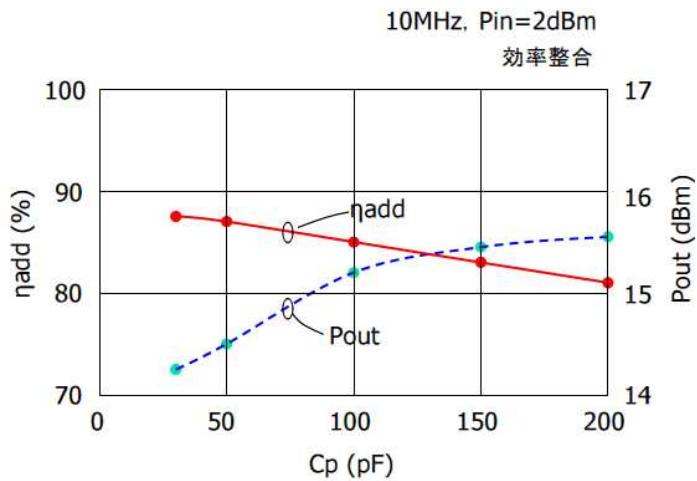

なお、E級動作、10MHzの場合の $C_P$ の値は、ロードプルシミュレーションにより得られた $C_P$ 対 $\eta_{add}$ ,  $P_{out}$ 特性（図3.33）から、 $C_P = 50 pF$ とした。一方、E級動作、2GHzの場合にはFETのドレインソース間容量 $C_{ds}$ を $C_P$ の代わりに用いることとしている（従って、FETの外に $C_P$ は装荷されていない）。

周波数10MHzの場合、各動作級の電流、電圧波形はほぼ理論で示された波形となり、また、FETに電流が流れている時には電圧は0, FETに0でない電圧がかかっている時には電流は0となっている。また負荷線特性から、 $V_{max}$ の値はF級<F<sup>-1</sup>級<E級の順で増大し、ほぼ理論と同じ結果となっている。

周波数2GHzの場合も同様な特性となる。ただし、電流、電圧波形はFET内の寄生サセプタンスの影響により、少し崩れた特性となり、また、電流と電圧が共に0とならない領域が増加する傾向を持つようになる。

表3.2に周波数10MHzの場合の効率および出力特性をまとめて示す。なお、表には、比較のため、高調波にたいするインピーダンス $Z_n$ ( $n = 2 \square 5$ )条件を $0\Omega$ (short),  $50\Omega$ ,  $\infty\Omega$ (open)と変化させて計算を行ったものを示している、F, F<sup>-1</sup>, E級の動作条件の時に高効率となっている。

表3.3に周波数2GHzの場合の同様の特性をまとめて示す。周波数10MHzの場合と同様の傾向が得られている。

(b) F級動作, 2GHz の場合

図3.30 F級動作シミュレーション

図3.31  $F^{-1}$ 級動作シミュレーション

(a) E級動作, 10MHz の場合

(b) E級動作, 2GHz の場合

図3.32 E級動作シミュレーション

図 3.33 E 級動作, 10MHz における,  $C_P$  対  $\eta_{add}$ ,  $P_{out}$  特性

表3.2 周波数10MHz の場合の効率および出力特性まとめ

@ Pin=2dBm

| even<br>odd \ even | Short               | 50Ω              | Open                               |

|--------------------|---------------------|------------------|------------------------------------|

| Short              | B級 62.1%<br>17.2dBm | 67.2%<br>15.3dBm | F <sup>-1</sup> 級 86.1%<br>14.4dBm |

| 50Ω                | 73.8%<br>17.0dBm    | 70.3%<br>15.2dBm | 83.4%<br>12.7dBm                   |

| Open               | F級 86.1%<br>15.5dBm | 78.5%<br>13.5dBm | E級 87.0%<br>14.5dBm                |

表3.3 周波数2GHz の場合の効率および出力特性まとめ

@ Pin=6dBm

| even<br>odd \ even | Short               | 50Ω              | Open                               |

|--------------------|---------------------|------------------|------------------------------------|

| Short              | B級 57.1%<br>18.1dBm | 64.1%<br>16.6dBm | F <sup>-1</sup> 級 75.9%<br>15.6dBm |

| 50Ω                | 66.7%<br>18.0dBm    | 63.4%<br>16.2dBm | 71.6%<br>15.2dBm                   |

| Open               | F級 68.7%<br>18.0dBm | 62.4%<br>16.1dBm | E級 72.9%<br>15.7dBm                |

### 3.3 低歪み化

#### 3.3.1 増幅器の歪み発生メカニズム

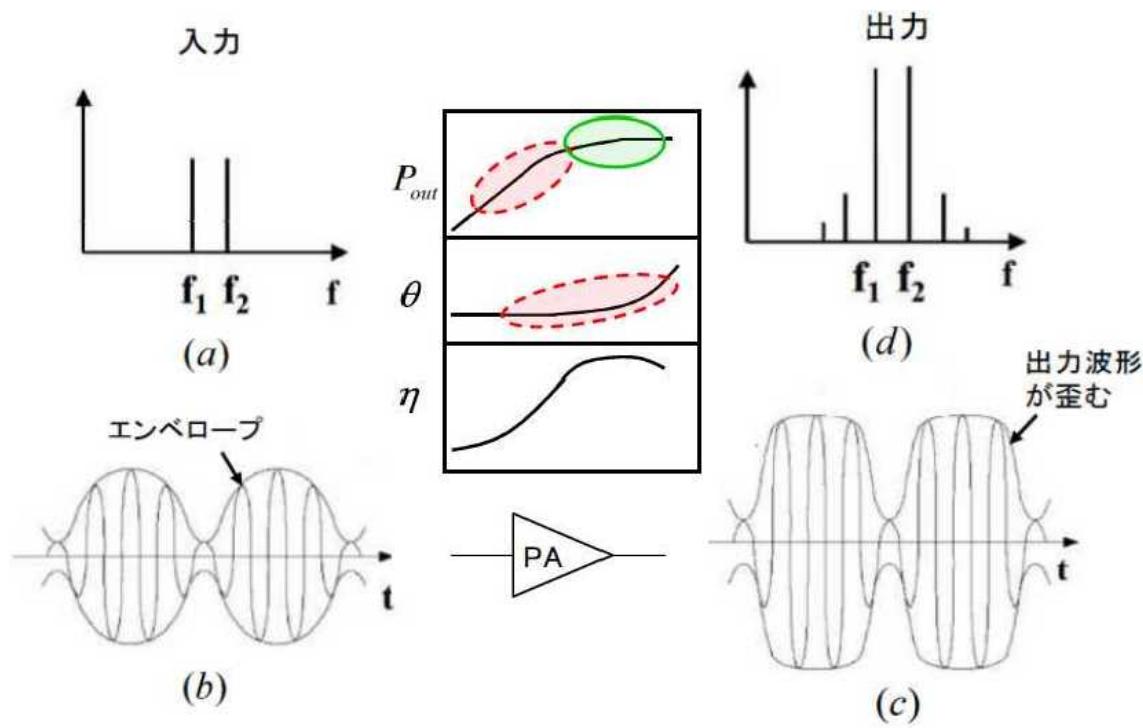

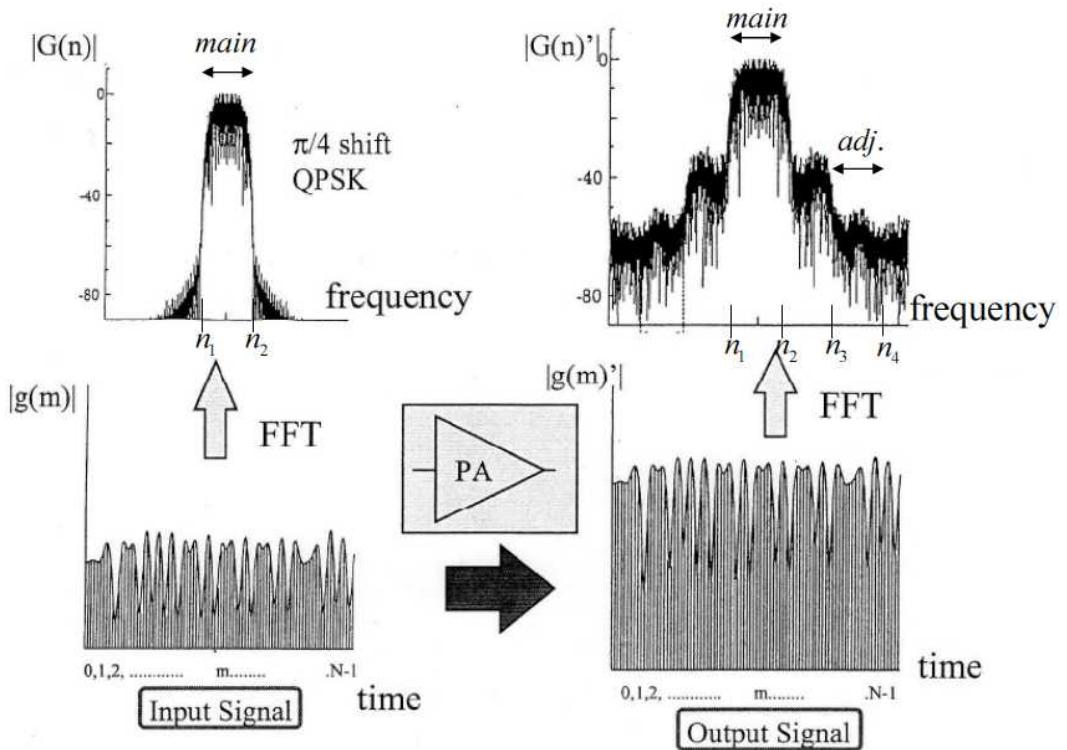

デジタル変調信号（QPSKやQAM変調信号など）やマルチキャリア信号（マルチキャリア共通増幅信号やOFDM変調信号など）では信号の振幅（エンベロープ）が時間とともに変動する。このようなエンベロープが時間変動する信号を増幅する場合、増幅器に振幅歪み（ $AM - AM$  変換）や位相歪み（ $AM - PM$  変換）があると、出力信号の振幅や位相に歪みの影響が現われ、信号品質が劣化したり、スペクトルの広がりによる他チャネルへの干渉が問題となったりする。図3.34に増幅器による歪み発生の様子を示す。

- ・効率と歪みはトレードオフの関係

- ・振幅・位相の非線形性 → 線形化(歪み補償)

- ・出力飽和によるクリッピング(PAPR問題) → 飽和出力アップ

図3.34 増幅器における歪み発生の様子

図において(a)は周波数軸で与えた入力信号のスペクトル、(b)は時間軸で与えた入力信号の時間波形であり、(a)と(b)はフーリエ変換で関係付けられる。

(c)は時間軸で与えた出力信号の時間波形であり、入力信号のエンベロープが時間により変動する場合、電力増幅器（PA）の振幅および位相歪により歪んだ波形となる。(d)は周波数軸で与えた出力信号スペクトルであり、波形歪みにより入力周波数以外の周波数成分を含むスペクトルとなる。(c)と(d)はフーリエ変換で関係付けられる。

増幅器における歪みは、(1) 出力飽和に至る前の増幅器の振幅・位相の非線形性によるもの（図の赤塗り部分）と(2) 出力飽和による信号振幅のクリッピングによるもの（図の緑塗り部分）があり、両者で低歪み化設計の手法が異なってくる（後述）。

図に示されるように、一般に、増幅器は小信号動作時には線形（低歪み）動作するが、そこでは効率が低い。一方、飽和に近い大信号動作時には高効率となるが、歪み性能が劣化する。低歪み増幅器の設計では、高効率と低歪み性能をいかに両立させるかが課題となる。

### 3.3.2 歪み評価パラメータと歪み特性シミュレーション<sup>[6]</sup>

実際の通信システムでは増幅器の歪み評価パラメータとして、(a)相互変調歪み（IM；Intermodulation）、(b)隣接チャネル漏洩電力（ACPR；Adjacent Channel Leakage Power Ratio）、(c)NPR（Noise Power Ratio）等が用いられる。これらを通常の非線形シミュレーション（SPICE, Voltera Series, Harmonic Balance 等）で計算することは膨大な計算処理が必要となり非現実的である。

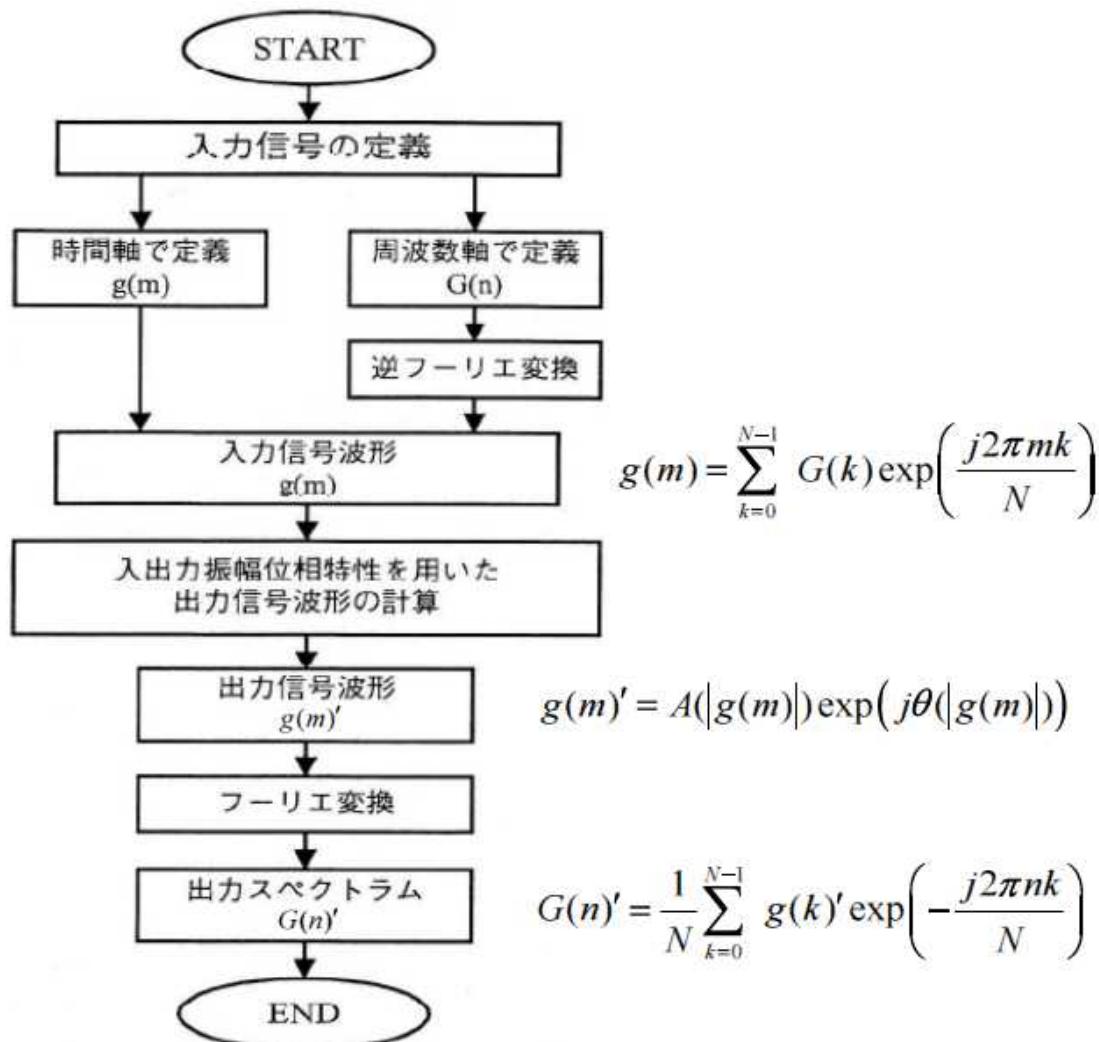

これに変わる歪み特性のシミュレーション方法として、Envelope Simulationがある。これは単一の無変調（CW）信号で測定（または計算）された増幅器の振幅/位相の歪み特性（AM-AM / AM-PM 変換）とフーリエ変換（実際には離散フーリエ変換）とを組み合わせ用いて解析するものである。

増幅器の入力信号の複素電圧を  $V_{in}(t)$ 、出力信号の複素電圧を  $V_{out}(t)$  とする

と、これらは以下で関係付けられる。

$$V_{in}(t) = \rho \cdot \exp(j\omega t) \quad (3.67)$$

$$V_{out}(t) = A(|\rho|) \cdot \exp(j\omega t + j\theta(|\rho|)) \quad (3.68)$$

ここで、 $\rho$  は入力信号の複素電圧振幅、 $A(|\rho|)$  は出力信号の複素電圧振幅であ

り  $|\rho|$  に依存す、 $\theta(|\rho|)$  は出力信号の位相変化特性であり  $|\rho|$  に依存する。

$A(|\rho|)$ 、 $\theta(|\rho|)$  は、無変調 (CW) 信号で測定 (または計算) された増幅器の入出力振幅・位相特性である。式(3.68)で与えられる出力信号電圧  $V_{out}(t)$  をフーリエ変換することにより出力信号スペクトルが得られる。図3.35に、Envelope Simulationによる歪み特性の計算フローを示す。

図3.35 Envelope Simulationによる歪み特性の計算フロー

周波数軸での入力信号（複素）電圧を  $G(n)$  ( $n = 0, 1, 2, \dots, N-1$ ) , 時間軸での入力信号（複素）電圧を  $g(m)$  ( $m = 0, 1, 2, \dots, N-1$ ) とすると, これらは次式の離散フーリエ変換で関係付けられる。

$$\left. \begin{aligned} g(m) &= \sum_{k=0}^{N-1} G(k) \cdot \exp\left(j2\pi k \frac{m}{N}\right) \\ G(n) &= \frac{1}{N} \sum_{k=0}^{N-1} g(k) \cdot \exp\left(-j2\pi k \frac{n}{N}\right) \end{aligned} \right\} \quad (3.69)$$

増幅された時間軸での出力信号電圧  $g(m)'$  は, 式 (3.67) , (3.68) の関係を用いて, 次式で与えられる。

$$g(m)' = A(|g(m)|) \exp(j\theta(|g(m)|)) \quad (3.70)$$

$g(m)'$  を次式で離散フーリエ変換することにより, 周波数軸での出力信号電圧  $G(n)'$  が求まる。  $G(n)'$  が出力スペクトルを表わす。

$$G(n)' = \frac{1}{N} \sum_{k=0}^{N-1} g(k)' \cdot \exp\left(-j2\pi k \frac{n}{N}\right) \quad (3.71)$$

以下で, 歪み評価パラメータである(a) 相互変調歪み  $IM$  , (b) 隣接チャネル漏洩電力  $ACPR$  , (c)  $NPR$  の計算例を示す。

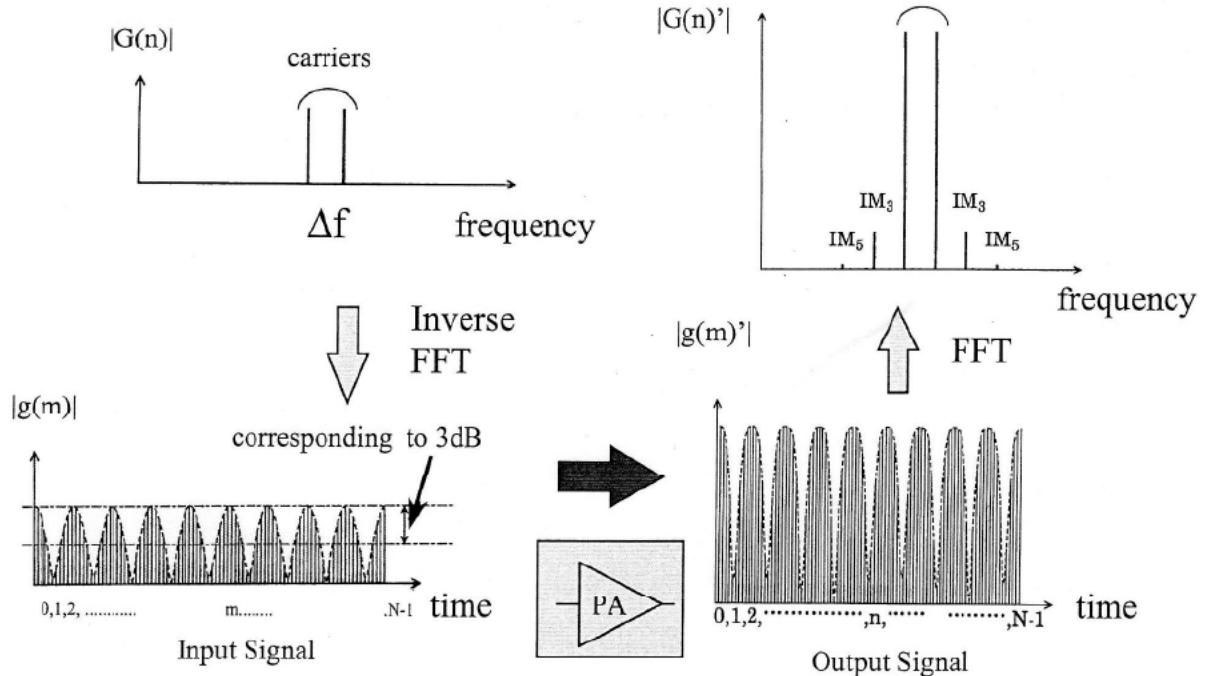

(a) 相互変調歪み ( $IM$  ; Intermodulation)

相互変調歪みは周波数間隔の狭い2波のCW波でなる信号を増幅した場合に生じるスペクトルの広がりを示す歪み評価パラメータである。2波の周波数が  $f_1$ ,

$f_2$  とすると、 $f_1, f_2$  の信号成分の近傍に  $2f_1 - f_2, 2f_2 - f_1$ , や,  $3f_1 - 2f_2$ ,  $3f_2 - 2f_1$  の歪み成分が生じ、スペクトルが広がる。信号成分と  $2f_1 - f_2$ ,  $2f_2 - f_1$  の歪み成分の電力比を3次相互変調歪み  $IM_3$ ，信号成分と  $3f_1 - 2f_2$ ,  $3f_2 - 2f_1$  の歪み成分の電力比を5次相互変調歪み  $IM_5$  と呼ぶ。図3.36に、2波のCW波でなる信号  $G(n)$  を与えた時の相互変調歪み  $IM$  の計算例を示す。

図3.36 2波のCW波でなる信号  $G(n)$  を与えた時の  $IM$  の計算

周波数軸で与えられた入力信号  $G(n)$  は式(3.69)に従い時間軸信号  $g(m)$  に変換される。 $g(m)$  は周波数差  $\Delta f = f_2 - f_1$  の1/2の周期でエンベロープが変動する信号となる。エンベロープのピーク電力は平均電力の2倍（3 dBアップ）の値となる。これは、2波のCW波でなる信号を増幅する場合、平均電力より3 dB高

いレベルまでの振幅および位相歪みの影響を受けることを意味する。次に、式(3. 70)から増幅された時間軸信号  $g(m)'$  が計算される。さらに、 $g(m)'$  は式(3. 71)に従いフーリエ変換され、周波数軸信号  $G(n)'$  が得られる。 $G(n)'$  は  $IM$  歪み ( $IM_3$ ,  $IM_5$ ) 成分を含むスペクトルとなっている。

(b) 隣接チャネル漏洩電力 ( $ACPR$ ; Adjacent Channel Leakage Power Ratio)

隣接チャネル漏洩電力  $ACPR$  はデジタル変調信号を増幅した時に生じるスペクトルの広がりにより隣接するチャネルに干渉波として漏洩する電力を表わす歪み評価パラメータである。

デジタル変調信号（電圧） $V_{in}(t)$  は、キャリア周波数  $\omega$  のRF信号が（ナイキストフィルタにより波形成形された）I, Qチャネルのベースバンド信号  $I(t)$ ,  $Q(t)$  で変調されており以下で表わせる。

$$V_{in}(t) = (I(t) + jQ(t)) \exp(j\omega t) \quad (3.72)$$

信号のエンベロープは  $\sqrt{I(t)^2 + Q(t)^2}$  で時間変動するため、増幅器の振幅/位相歪み特性により出力信号（電圧） $V_{out}(t)$  が歪む。デジタル変調信号のエンベロープのピーク電力と平均電力の比は  $PAPR$  (Peak to average power ratio) と呼ばれ、例えばQPSKの場合には2dB程度、16QAMの場合には4.6dB程度となる（8章、表8.1参照）。

図3.37に、 $\pi/4$ -shift QPSK変調信号の時間波形  $g(m)$  を与えた時の  $ACPR$  の計算例を示す。

図3.37  $\pi/4$ -shift QPSK変調信号  $g(m)$  を与えた時のACPRの計算

式(3.72)で示される入力信号をサンプリングした時間軸信号を  $g(m)$  とする。

$g(m)$  を式(3.69)に従いフーリエ変換することにより、周波数軸に対する信号、すなわちスペクトル  $G(n)$  が求まる。入力信号は、ベースバンド信号  $I(t)$ ,  $Q(t)$  により決まる占有帯域幅を有している。式(3.70)から増幅された時間軸信号  $g(m)'$  が計算される。さらに、 $g(m)'$  は式(3.71)に従いフーリエ変換され、周波数軸信号  $G(n)'$  が得られる。ACPRは自チャンネルの信号電力  $P_{main}$  と隣接チャンネルへの漏洩電力  $P_{adj.}$  の比で定義される。 $G(n)'$  を用いてACPRは次式より計算される。

$$ACPR[dB] = 10 \log \left( \frac{P_{adj.}}{P_{main}} \right) = 10 \log \left( \frac{\sum_{n=n_3}^{n_4} |G(n)'|^2}{\sum_{n=n_1}^{n_2} |G(n)'|^2} \right) \quad (3.73)$$

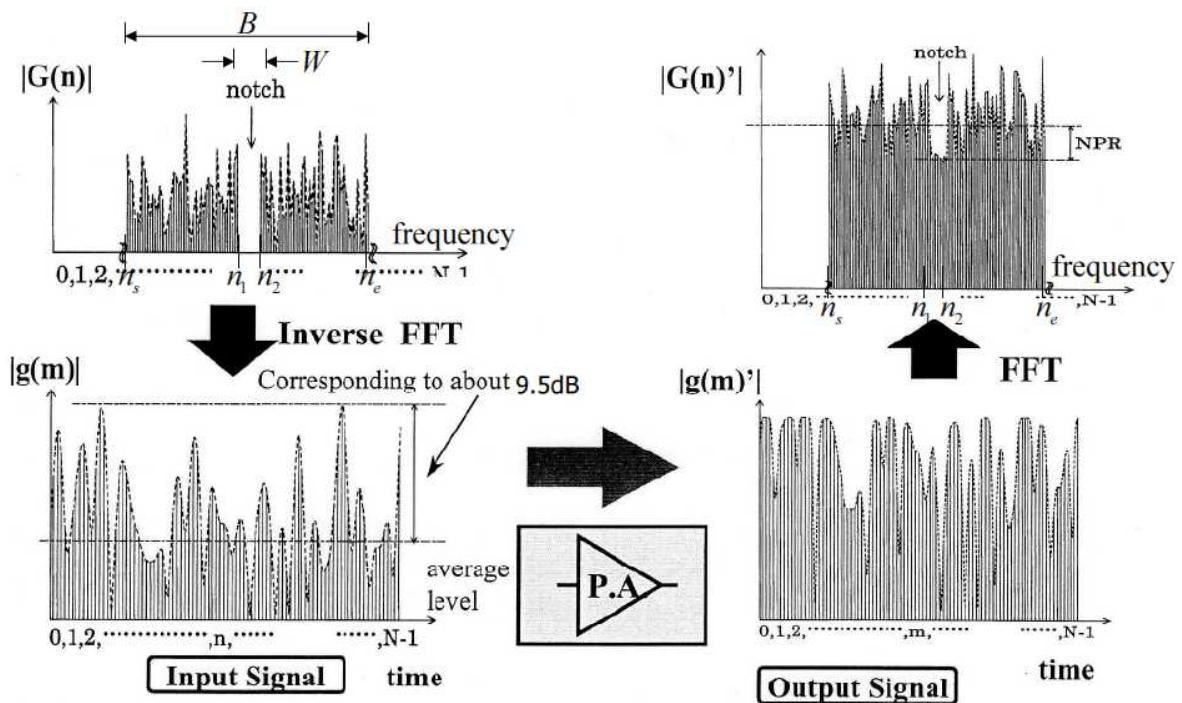

(c) *NPR* (Noise Power Ratio)

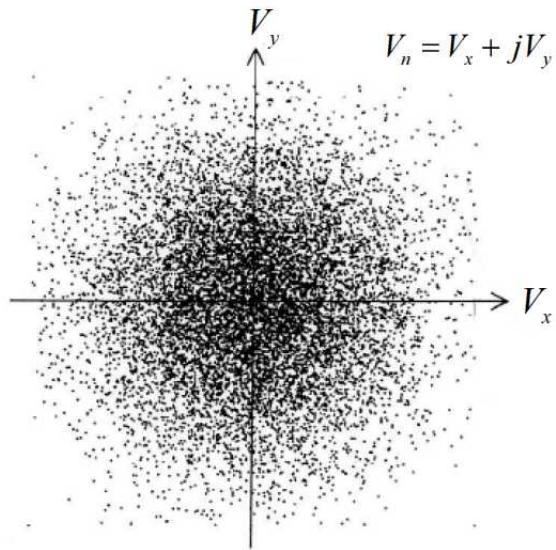

*NPR* (Noise Power Ratio) は入力信号にマルチキャリア信号に見立てたホワイトノイズを用い、ホワイトノイズの電力密度と歪み電力の電力密度の比として定義される。測定および解析において、入力信号は狭帯域のノッチを有するホワイトノイズとして与えられ、歪みによる電力はノッチの帯域内に落ち込む電力として取り扱われる。

ホワイトノイズは、周波数に依存しない、一定の電力スペクトルを持つ雑音である。しかし、瞬時に見た時ホワイトノイズは、全くランダムな振幅、位相を持った信号の集まりになっている。図3.38に複素平面上に表わしたホワイトノイズの電圧分布を示す。

図3.38 複素平面上に表わしたホワイトノイズの電圧分布

瞬時雑音を表わす雑音電圧  $V_n$  は複素平面上の電圧  $V_x$ ,  $V_y$  を使って次式で与えられる。

$$V_n = V_x + jV_y \quad (3.74)$$

$V_x, V_y$  はそれぞれガウス分布しており、確率密度関数  $P_x(V_x), P_y(V_y)$  は次式で与えられる。

$$P_x(V_x) = \frac{1}{\sqrt{2\pi}\sigma_x} \exp\left(-\frac{V_x^2}{2\sigma_x^2}\right) \quad (3.75)$$

$$P_y(V_y) = \frac{1}{\sqrt{2\pi}\sigma_y} \exp\left(-\frac{V_y^2}{2\sigma_y^2}\right) \quad (3.76)$$

$$\sigma_x^2 = \sigma_y^2 = \frac{\sigma_n^2}{2} \quad (3.77)$$

ここで、 $\sigma_x^2, \sigma_y^2$  はそれぞれ  $V_x, V_y$  の分散

この時、複素平面上の雑音電圧  $V_n$  の確率密度関数  $P_n(V_n)$  は、 $V_x, V_y$  が相関を持たないことから次式で与えられる。

$$P_n(V_n) = P_x(V_x)P_y(V_y) \quad (3.78)$$

雑音の平均電力  $\overline{|V_n|^2}$  は、定義より次式で与えられる。

$$\begin{aligned} \overline{|V_n|^2} &= \int |V_n|^2 P_n(V_n) dV_n \\ &= \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} (V_x^2 + V_y^2) P_x(V_x) P_y(V_y) dV_x dV_y \\ &= \int_{-\infty}^{\infty} V_x^2 P_x(V_x) dV_x + \int_{-\infty}^{\infty} V_y^2 P_y(V_y) dV_y \\ &= \sigma_x^2 + \sigma_y^2 = \sigma_n^2 \end{aligned} \quad (3.79)$$

$V_n$ はガウス分布していることから、 $3\sigma_n$ のレンジに $V_n$ の99%が含まれると考え

られる。今、 $3\sigma_n$ に相当するホワイトノイズの電圧を $V_{np}$ とすると、次式より

$|V_{np}|^2$ は平均電力 $\overline{|V_n|^2}$ に比べて約9.5 dB高くなる。

$$\begin{aligned} 10 \log(|V_{np}|^2) &= 10 \log((3\sigma_n)^2) = 10 \log(\sigma_n^2) + 10 \log(9) \\ &= 10 \log(\overline{|V_n|^2}) + 9.5 \end{aligned} \quad (3.80)$$

ホワイトノイズに対してこのようなモデル化を行った後、先のIMを算出する場合と同様の計算を行うことによりNPRが計算される。図3.39にノッチ付きホワイトノイズを用いた場合のNPRの計算例を示す。

図3.39 ノッチ付きホワイトノイズを用いた場合のNPrの計算

まず、周波数軸上の入力信号  $G(n)$  を、帯域  $W (= n_2 - n_1)$  のノッチを有し、

$B (= n_e - n_s)$  の帯域を有するホワイトノイズとして与える。すなわち、帯域  $B$  内

の各サンプル点にランダムな複素電圧  $V_n$  を対応させる。ただし、 $V_n$  の確率密度

関数  $P_n(V_n)$  は式 (3.75) ~ (3.78) に従う。周波数軸で与えられた入力信号  $G(n)$

は式 (3.69) に従い時間軸信号  $g(m)$  に変換される。確率過程理論から、 $G(n)$  が

ガウス分布している時、式 (3.69) のように  $G(n)$  の線形結合で与えられる  $g(m)$

もまたガウス分布している。次に、式 (3.70) から増幅された時間軸上の出力信

号  $g(m)'$  が計算される。さらに、 $g(m)'$  は式 (3.71) に従いフーリエ変換され、

周波数軸信号  $G(n)'$  が得られる。 $NPR$  は次式に従い算出される。

$$NPR = 10 \log \left( \frac{P_1}{P_2} \right) \quad (3.81)$$

ただし、

$$P_1 = \frac{\sum_{n=n_1}^{n_2} |G(n)|^2}{n_2 - n_1}, \quad P_2 = \frac{\left( \sum_{n=n_s}^{n_1-1} + \sum_{n=n_2+1}^{n_e} \right) |G(n)|^2}{n_e - n_s - (n_2 - n_1)}$$

### 3.3.3 歪み補償

増幅器により生じる歪みのうち、増幅器が出力飽和に至る前の振幅/位相の非

線形性によって生じるものについては各種歪み補償による線形化により補償で

きる。図3.40に歪み補償方式をまとめて示す。歪み補償は大きく、プレディス

トーション、フィードバック、フィードフォワードに分類される。また、プレ

ディストーション歪み補償にはアナログ方式とデジタル方式がある。これらの

歪み補償は、性能やコストなどの目的に応じて使い分けられる。

| 歪み補償方式  | プレディストーション |      | フィードバック | フィードフォワード |

|---------|------------|------|---------|-----------|

|         | アナログ       | デジタル |         |           |

| 歪み補償量   | 小/中        | 大    | 中/大     | 大         |

| 補償を行う信号 | RF/IF      | デジタル | IF/BB   | RF        |

| 回路規模    | 小/中        | 中/大  | 中/大     | 中/大       |

| 構成      |            |      |         |           |

図 3.40 歪み補償方式

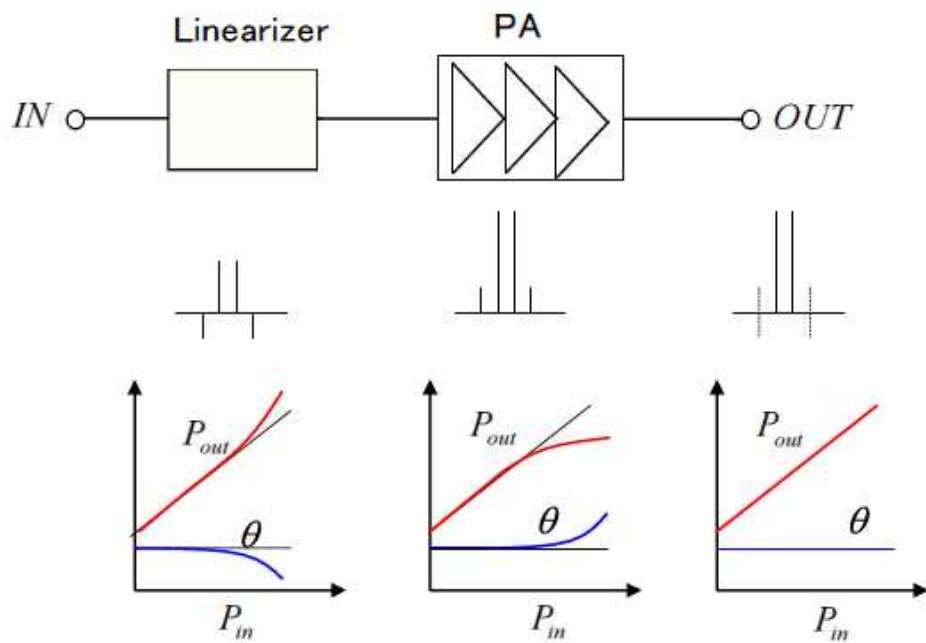

### (1) アナログプレディストーション歪み補償

図 3.41 にアナログプレディストーション歪み補償の原理を示す。

図 3.41 アナログプレディストーション歪み補償の原理

電力増幅器 (PA) で発生する歪みに対して逆特性の歪みを前もって発生させて

おいて系全体では歪みを低減するものである。振幅/位相特性で表現すれば、PAと逆の振幅/位相特性を前もって作っておき系全体で振幅/位相特性の線形化を図るものとみることもできる。逆特性の歪みを発生させる回路はアナログ素子を用いて構成され、アナログプレディストータと呼ばれる。また、PAとは別に独立に構成することができ、リニアライザとも呼ばれる。

アナログプレディストータ（リニアライザ）では、一般に非線形回路として、小電力のトランジスタ増幅器やダイオードなどが使われ、様々な構成が提案されている。

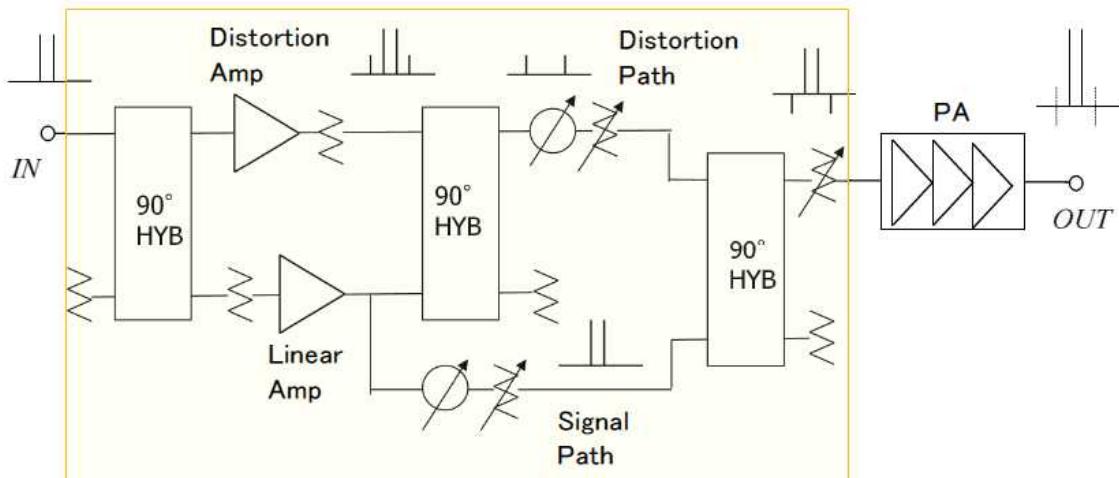

図 3.42 は、小電力増幅器を用いて構成され、RF 帯で動作するアナログプレディストータ（RF リニアライザ）<sup>[7]</sup>である。入力された信号は 2 つに分けられ、一方からは歪み増幅器（Distortion Amp）で歪みを含む増幅信号を発生させ、他方からは減衰器を介した線形増幅器（Linear Amp）で歪みを含まない増幅信号を発生させる。上記 2 つの経路の信号を合成して信号成分をキャンセルして歪み成分のみを抽出する。この歪み成分の振幅と位相を調整し、別経路からの歪みを含まない信号と合成することで、PA に対して逆特性の歪み成分を含んだ信号を発生することができる。

図 3.42 小電力増幅器を用いて構成された RF リニアライザ

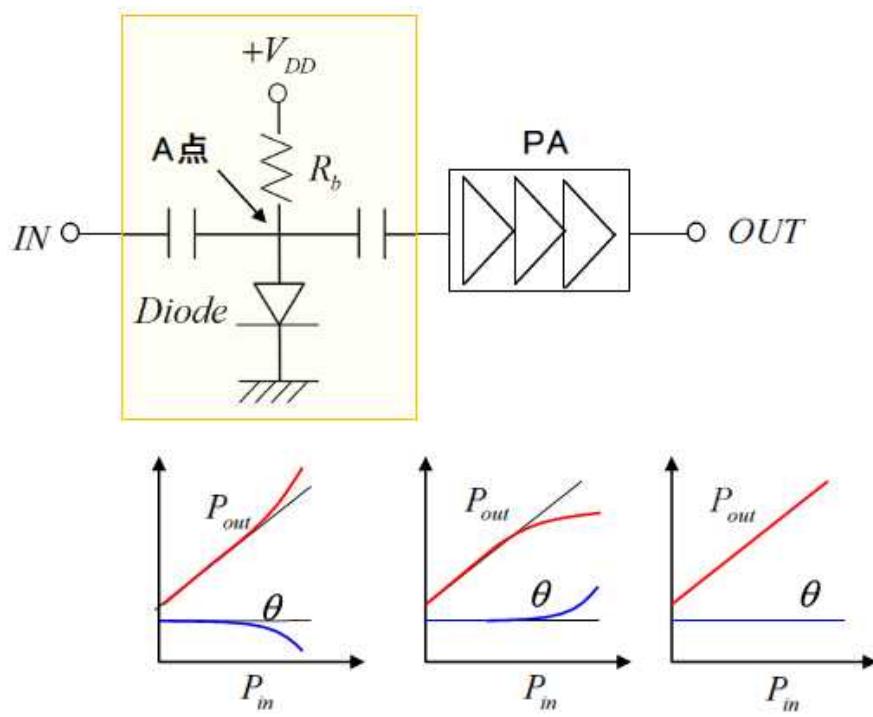

図 3.43 はダイオードを用いて簡易に構成された RF 帯で動作するアナログプレディストータ（RF リニアライザ）<sup>[8]</sup>である。1 個のダイオードとバイアス印加用の抵抗および DC カットコンデンサのみで構成される。入力信号のエンベロープに応じてダイオードの動作電圧（図の A 点の電圧）が変化し、これにより PA と逆の振幅/位相歪み特性が生み出される。

図 3.43 ダイオードを用いた簡易形 RF リニアライザ

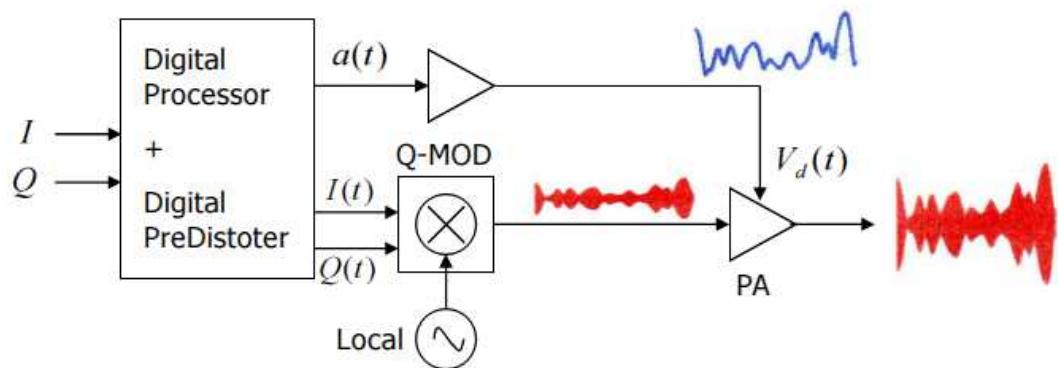

## (2) デジタルプレディストーション歪み補償

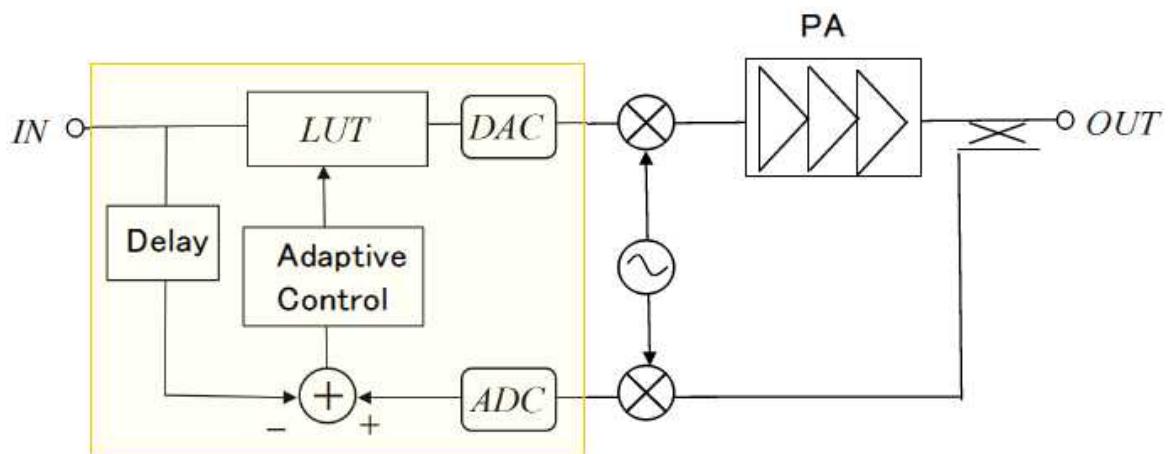

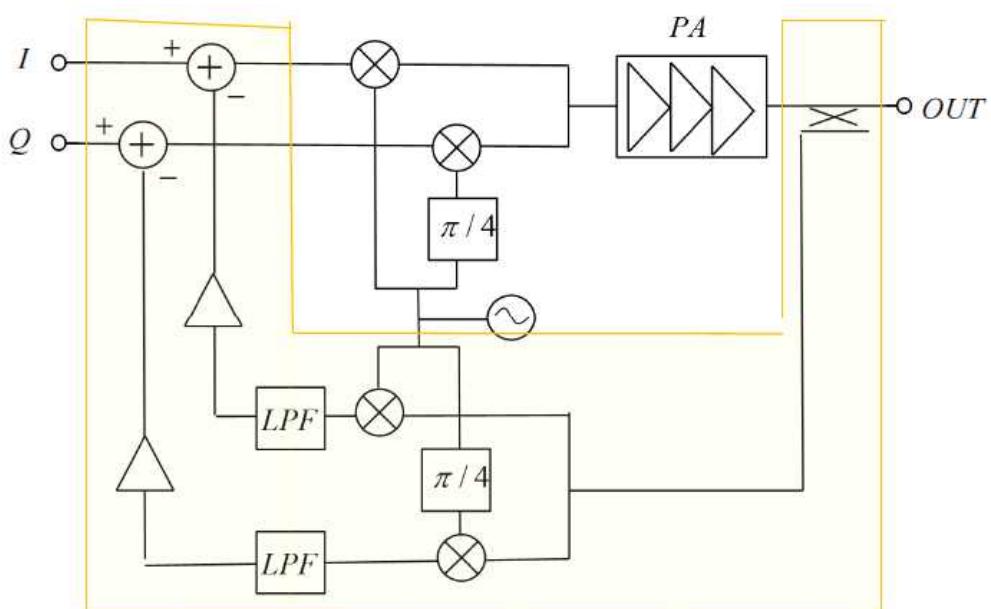

図 3.44 にデジタルプレディストーション歪み補償の回路構成例<sup>[9]</sup>を示す。ここに用いられるデジタルプレディストータは電力増幅器 (PA) と逆の振幅/位相歪み特性を有する信号をデジタル回路を用いて生み出すものである。

図 3.44 デジタルプレディストーション歪み補償の回路構成

デジタルプレディストータ内部には、入力された  $I, Q$  チャネルのベースバンドデジタル信号の値をインデックスとし補正係数を記入した  $LUT$  (Look Up Table) を有している。入力されたベースバンドデジタル信号の値に応じて、 $LUT$  からの補正係数を用いて入力信号を補正することで、PA と逆の振幅/位相歪み特性を有する信号を発生させる。さらに、一般には、PA の出力信号をデジタル信号に復調し、入力デジタル信号と比較することで系全体の歪みが小さくなるように  $LUT$  のデータを適応的に更新していくように構成される (ADPD ; Adaptive Digital Pre-Distorter)。

デジタルプレディストータでは内部の演算回路ならびに AD/DA コンバータなどが、取り扱う変調波の帯域（データ速度）に対して十分高速に動作する必要がある。

### (3) フィードバック歪み補償

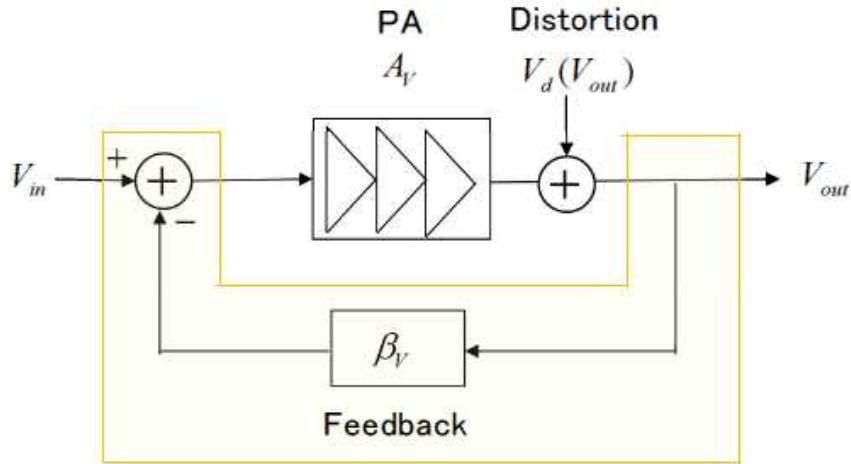

図 3.45 にフィードバック歪み補償の基本構成示す。

図 3.45 フィードバック歪み補償の原理図

入出力電圧を  $V_{in}$ ,  $V_{out}$  とし、増幅器の（電圧）利得を  $A_v$ 、帰還係数を  $\beta_v$  とし負帰還される。出力電圧  $V_{out}$  に応じて歪み電圧  $V_d(V_{out})$  が生じるとする。

フィードバックが無い場合、 $V_{out}$  は次式で表わせる。

$$V_{out} = A_v V_{in} + V_d(V_{out}) \quad (3.82)$$

これに対して、フィードバックがある場合、 $V_{out}$ は次式で表わせる。

$$\begin{aligned} V_{out} &= A_v(V_{in} - \beta_v V_{out}) + V_d(V_{out}) \\ \rightarrow V_{out} &= \frac{A_v}{1+A_v\beta_v} V_{in} + \frac{1}{1+A_v\beta_v} V_d(V_{out}) \end{aligned} \quad (3.83)$$

フィードバック（負帰還）により、利得は  $\frac{1}{1+A_v\beta_v}$  ( $\leq 1$ ) 倍だけ低下する。ここ

で、利得が低下した分だけ入力電圧を  $V_{in} \rightarrow V'_{in} = V_{in}(1+A_v\beta_v)$  に増大すると、出力電圧はフィードバックが無い場合と同じ大きさになり、次式が得られる。

$$\begin{aligned} V_{out} &= \frac{A_v}{1+A_v\beta_v} V'_{in} + \frac{1}{1+A_v\beta_v} V_d(V_{out}) \\ &= A_v V_{in} + \frac{1}{1+A_v\beta_v} V_d(V_{out}) \end{aligned} \quad (3.84)$$

式 (3.82) と (3.84) の比較から、フィードバックにより、同一出力時の歪み

電圧が  $\frac{1}{1+A_v\beta_v}$  ( $\leq 1$ ) 倍になり、歪みが低減される。フィードバック歪み補償系

では、クローズドループで自動的に制御が行われることになり、原理上はその他の制御回路などは不要となる利点を有する。

ところで、キャリア (RF) 信号に対して直接フィードバック系を構成することは、增幅回路やフィードバック回路による位相変化が大きく、正のフィードバック（正帰還）となって発振する可能性などの問題がある。このため、通常、フィードバック系は IF 帯やベースバンド周波数に対して構成される。

図 3.46 はカルテシアンループを用いたフィードバック歪み補償の回路構成を示す<sup>[10]</sup>。この方式では、電力増幅器 (PA) からの出力信号の一部が直交復調され、 $I$ ,  $Q$  チャネルのベースバンドアナログ信号  $I(t)$ ,  $Q(t)$  のそれぞれに対するフィードバックループが構成される。

フィードバック系では、自身の信号波を用いて自動的に歪み補償制御を行うことができるという他の補償系にない特長を有する。これから、カルテシアンループを用いたフィードバック歪み補償は比較的狭帯域のデジタル変調波を用いる通信システム端末に用いられることが多い。ただし、フィードバックループは変調波の変化、すなわちエンベロープの変化にたいしてリアルタイムで動作する必要があるので変調波の帯域が広くなった場合には、安定にフィードバック系を構成することが難しくなる。

図 3.46 カルテシアンループを用いたフィードバック歪み補償の回路構成

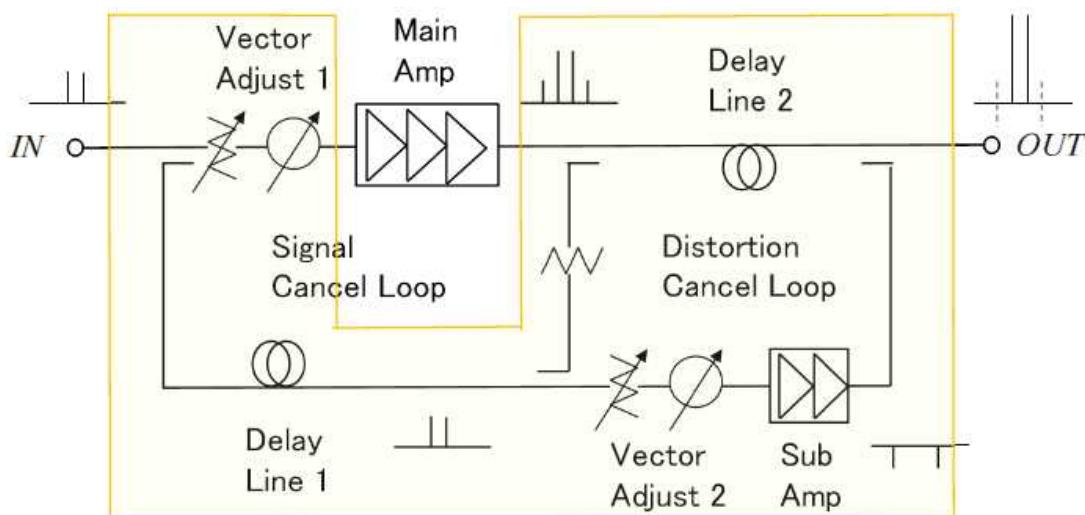

#### (4) フィードフォワード歪み補償

図 3.47 にフィードフォワード歪み補償（増幅器）の構成を示す<sup>[11]</sup>。入力信号は 2 つの経路に分けられ、一方は主増幅器 (Main Amp) で増幅される。入力信号の他方は、遅延線路 (Delay Line 1) を通過した後、主増幅器の一部と信号成分が逆相・等振幅となるように合成され、歪み成分が抽出される。抽出された歪み成分は副増幅器 (Sub Amp) で増幅される。この歪み成分は主増幅器から

の出力信号と歪み成分が逆相・等振幅になるように合成される。これにより、出力における歪み成分が打ち消され、低歪み化が図れる。

フィードフォワード歪み補償（増幅器）は2つのループからなり、主増幅器を含む前側のループは信号キャンセルループ（あるいは歪み抽出ループ）、副増幅器を含む後側のループは歪みキャンセルループと呼ばれる。広帯域にわたって良好な歪み補償ができるようにするため、信号キャンセルループおよび歪みキャンセルループに遅延線路（Delay Line 1, 2）が必要となる。

図 3.47 フィードフォワード歪み補償（増幅器）の構成

フィードフォワード歪み補償（増幅器）では主増幅器で発生した歪みを使って補償を行うので、広帯域、高ダイナミックレンジにわたって良好な歪み補償性能が得られることが期待できる。また、フィードバック方式のような安定性の問題が発生しないので、広帯域な変調波やマルチキャリア信号を用いる場合にも用いることが出来る。一方、問題点としては、歪みキャンセルループに副増幅器や遅延線路（Delay Line 2）が必要なことから、消費電力が大きくなること、系全体が大形で高コストとなること等があげられる。

フィードフォワード歪み補償（増幅器）は、消費電力や寸法に対して比較的余裕があるマルチキャリア用の移動体通信基地局などで使われることが多い。

### 3.3.4 出力飽和による歪みへの対応

増幅器による歪が、出力飽和による信号振幅のクリッピングによるものである場合には、先に述べた歪み補償では歪みを低減することが出来ない。この場

合に低歪み（かつ高効率）を実現する方法として（1）増幅器の動作点を飽和レベルから *PAPR* 分バックオフさせるとともにバックオフ動作点での効率を向上させること、（2）増幅器を飽和点で用いるがそれでも歪みが発生しない方法をとることがある。（1）の方法としてドハティ増幅器<sup>[12]</sup>があり、（2）の方法として、LINC<sup>[13]</sup>、EER<sup>[14]</sup>、ET<sup>[15]</sup>等の方法が提案されている。

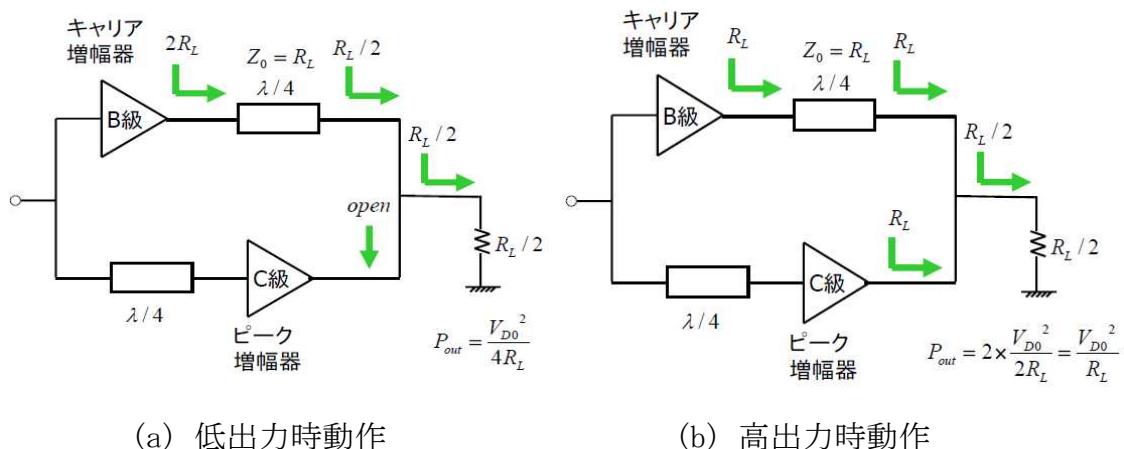

### （1）ドハティ増幅器

図3.48(a), (b)にドハティ増幅器の基本構成と動作を示す。B級バイアスされ小信号レベルから動作するキャリア増幅器と、C級バイアスされ大信号レベルになって動作開始するピーク増幅器とを用いて構成される。図の(a)は低出力時の動作を、(b)は高出力時の動作を示す。(a)ではキャリア増幅器のみが動作していて、ピーク増幅器は動作しておらずその出力インピーダンスはオープンになっている。この時、キャリア増幅器から負荷側を見込むインピーダンスは  $2R_L$  (効率整合負荷) となり、負荷に出力される電力は  $V_{D0}^2 / 4R_L$  となっている。一方、(b)では、ピーク増幅器もキャリア増幅器と同等の出力レベルで動作し、これらの出力は同相合成される。この時、それぞれの増幅器から負荷を見込むインピーダンスは  $R_L$  (出力整合負荷) となり、各増幅器から出力される電力は  $V_{D0}^2 / 2R_L$  となる。その結果、負荷に出力される電力は  $V_{D0}^2 / R_L$  となる。(b)の場合の出力は(a)の場合のそれに比べ4倍(6dBアップ)となっている。

図3.48 ドハティ増幅器の基本構成と動作

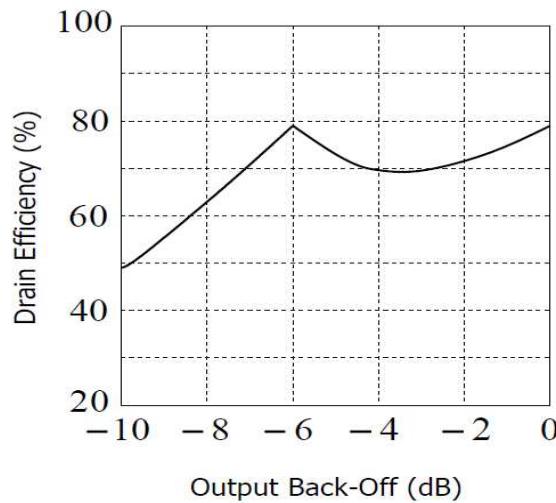

図3.49は理想状態でのドハティ増幅器のバックオフ出力と効率との関係を模式的に示すものである。飽和から6dBバックオフを取った動作点での効率はB級動作するキャリア増幅器の効率であり、理想的には78.5%となる。一方、6 dBアップのピーク電力までクリッピング無しで増幅される。

図3.49 ドハティ増幅器の効率特性

ドハティ増幅器では、振幅のクリッピングによる歪み発生を防ぐためバックオフをとて動作させるとともに、バックオフ動作時にも高い効率を実現することが主目的である。低歪み化のためには先の歪み補償手法と組み合わせ使うことが不可欠である。

## (2) LINC

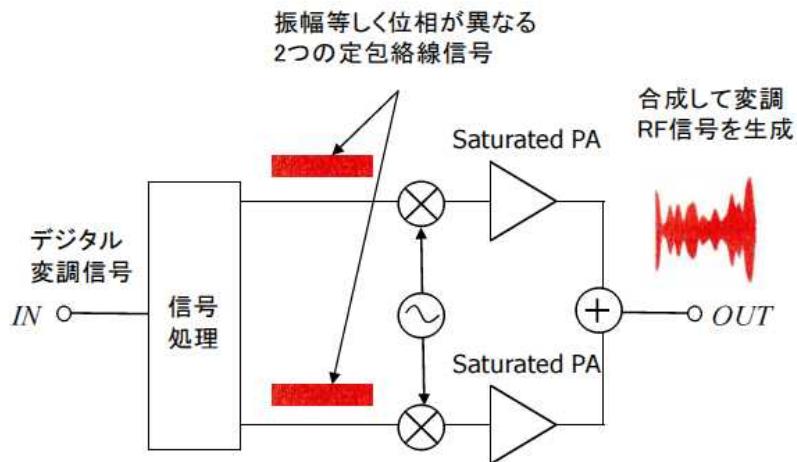

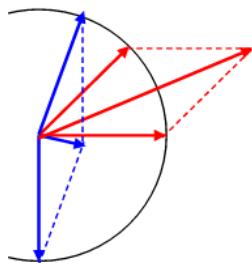

図3.50にLINC(Linear Amplification using Nonlinear Component)の構成と動作を示す。2個の飽和動作する電力増幅器(PA)を用いてその出力を合成する際に2つの出力波の位相関係により入力信号と相似の変調信号を作り出すものである。

入力の変調波を、定振幅で位相関係が変化する2つの信号波に分解するのはデジタル回路による信号処理で行われる。各PAは常に（エンベロープが時間変動しない）定包絡線信号で飽和動作しており、PA自身の歪みは原理的に発生しない。それにより結果的に低歪みが実現される。

図3.51に2つの一定振幅の出力波を合成してエンベロープが変化する出力変調信号波を作り出す様子を示す。2つのPAはいずれも常に飽和動作しているの

でそれぞれの効率は高い。しかし、出力信号波の振幅は2つのPAからの出力波の位相関係で作り出されるため合成の際に無効電力が存在することになる。これは合成器内のダミーロードで消費され、出力電力に寄与せず、その分効率が低下する。特に、*PAPR*の大きな信号を增幅する際にはこれが問題となる。LINC方式に原理的に内在する課題といえる。

図 3.50 LINC の構成と動作

図 3.51 2つの一定振幅の出力波を合成して出力変調信号波を作り出す様子

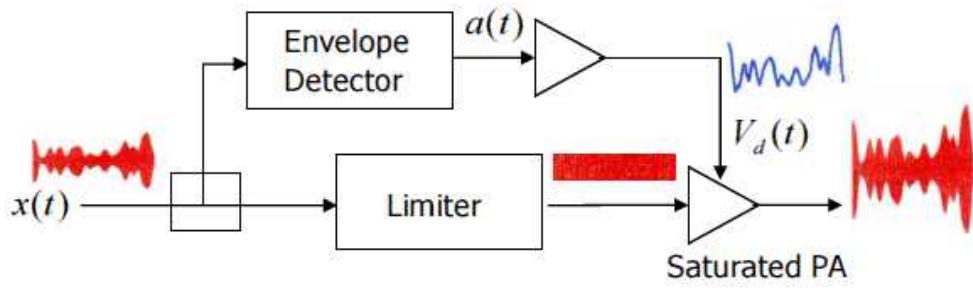

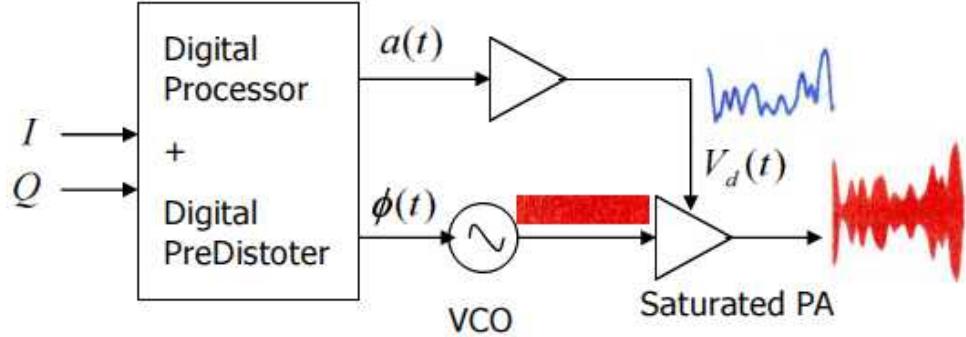

### (3) EER, ET

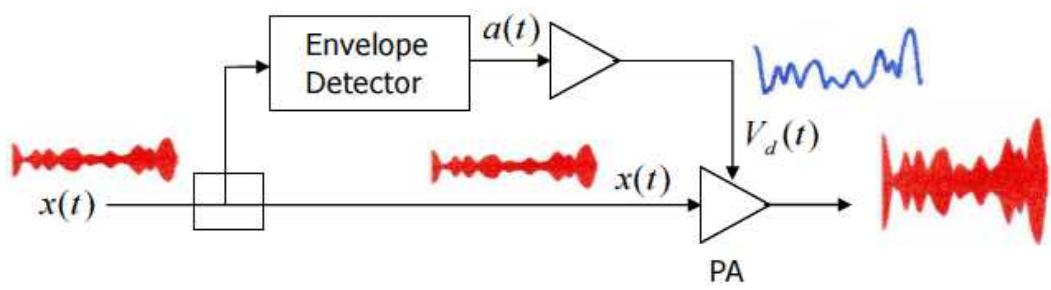

図 3.52(a), (b) に EER(Envelope Elimination and Restoration) の構成と動作を示す。(a) では入力変調信号から、定振幅で位相が変化する信号（定振幅・位相変調信号）と振幅エンベロープ情報を持った信号（エンベロープ信号）を抽出する。定振幅・位相変調信号は電力増幅器 (PA) に入力され飽和増幅される。一方 エンベロープ信号は低周波の高効率電力増幅器で増幅された後、PA のバイアス電圧として印加される。PA はバイアス電圧に応じた電力で飽和動作する

ことになり、これにより、PA 出力端で振幅および位相が入力変調信号と相似の出力変調信号が得られる。この時、PA は常に飽和出力で動作しており、高効率性能が得られることになる。図 3.52(b) は入力デジタル変調信号から直接定振幅・位相変調信号とエンベロープ信号を生み出すものである。

バイアス電圧のみにより変調信号の振幅情報を精度良く実現することは困難であり、歪み補償と組み合わせて用いられる必要がある。

(a) 変調信号をアナログで与える

(b) 変調信号をデジタルで与える

図 3.52 EER の構成と動作

EER と類似の発想による高効率化手法として図 8.53(a), (b) に示す ET (Envelope Tracking) がある。ET では、変調波の振幅に応じてバイアス電圧を変化させる点は EER と同じであるが、電力増幅器(PA)への入力信号については、振幅変化する変調信号をそのまま用いる。入力信号波の振幅に応じてバイアス電圧値を変化させることで高効率性能が得られるとともに、入力変調波をそのまま增幅するので歪み特性も良好となる。この場合にも、低歪み化のためには歪み補償と組み合わせて用いられるのが望ましい。

(a) 変調信号をアナログで与える

(b) 変調信号をデジタルで与える

図3.53 ETの構成と動作

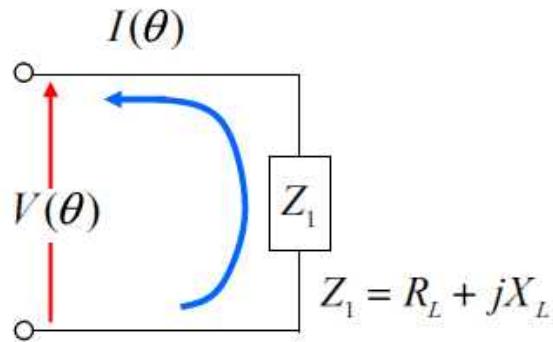

## 付録C 複素電圧 $V(\theta)$ , 電流 $I(\theta)$ とインピーダンス $Z_1 = R_L + jX_L$

図 C. 1 の回路において、インピーダンス  $Z_1 = R_L + jX_L$  は複素電圧  $V(\theta)$ , 複素電流  $I(\theta)$  を用いて以下で与えられる。なお、マイナス符号は電流の向きの関係で付けられている。

$$Z_1 = R_L + jX_L = -\frac{V(\theta)}{I(\theta)} \quad (\text{C. 1})$$

図 C. 1 インピーダンス  $Z_1 = R_L + jX_L$ , 複素電圧  $V(\theta)$ , 複素電流  $I(\theta)$

ここで、 $I(\theta) = I_{rf} e^{j\theta}$ ,  $V(\theta) = V_{rf} e^{j(\theta-\theta_0)}$  とすると、これらの実部が観測される電流、電圧となり、それぞれ次式で表わせる。

$$\operatorname{Re}(I(\theta)) = I_{rf} \cos \theta \quad (\text{C. 2})$$

$$\operatorname{Re}(V(\theta)) = V_{rf} \cos(\theta - \theta_0) = V_{ci} \cos \theta + V_{cq} \sin \theta \quad (\text{C. 3})$$

$$\text{ここで, } V_{ci} = V_{rf} \cos \theta_0, \quad V_{cq} = V_{rf} \sin \theta_0$$

これらを用いると、インピーダンス  $Z_1$  は以下のようにも表わすことが出来る。

$$\begin{aligned} Z_1 &= -\frac{V(\theta)}{I(\theta)} = -\frac{V_{rf} e^{j(\theta-\theta_0)}}{I_{rf} e^{j\theta}} = -\frac{V_{rf} \cos \theta_0}{I_{rf}} + j \frac{V_{rf} \sin \theta_0}{I_{rf}} \\ &= -\frac{V_{ci}}{I_{rf}} + j \frac{V_{cq}}{I_{rf}} \end{aligned} \quad (\text{C. 4})$$

式 (C. 1) との比較から次式が得られる。

$$R_L = -\frac{V_{ci}}{I_{rf}} \quad (\text{C. 5})$$

$$X_L = \frac{V_{cq}}{I_{rf}} \quad (\text{C. 6})$$