## 8. アナログ・デジタル変換器

### 8.1 アナログ・デジタル変換の概要

デジタル無線通信では、電波伝搬に RF (アナログ) 信号を用い、信号処理にデジタル信号を用いる。このため、受信機にはアナログをデジタルに変換する ADC (AD Converter)，送信機にはデジタルをアナログに変換する DAC (DA Converter) が必要となる。

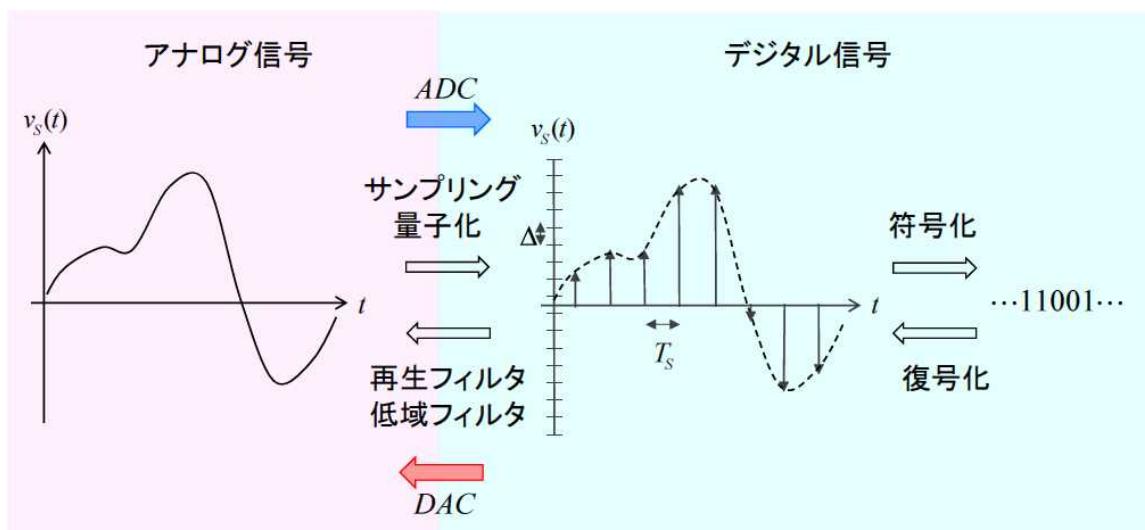

図 8.1 に ADC, DAC の機能概要を示す。ADC は連続なアナログ信号をサンプリング (標本化) および量子化し、さらに符号化し、バイナリ符号化デジタル信号を得るものである。一方、DAC はバイナリ符号化デジタル信号を復号化し、さらに再生および低域フィルタリングし、連続なアナログ信号を得るものである。

図 8.1 ADC/DAC の機能概要

#### 8.1.1 サンプリング (標本化)

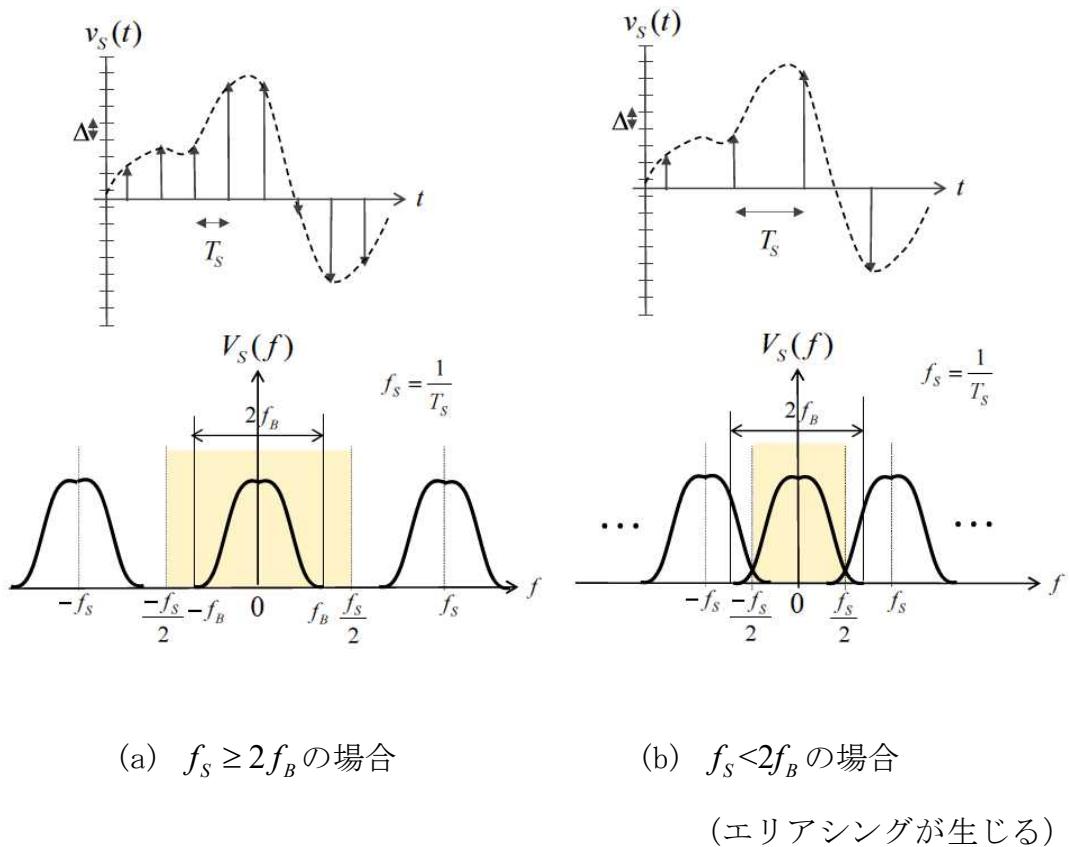

周波数帯域幅  $2f_B$  ( $-f_B \sim +f_B$ ) で帯域制限されたアナログ信号を時間間隔  $T_s$

( $=\frac{1}{f_s}$ ) でサンプリングすることを考える。ここで、 $f_s$  はサンプリング周波数である。図 8.2(a), (b) にサンプリングされた離散時間信号の時間波形とスペクトルを示す。サンプリングされた信号スペクトルは周波数  $nf_s$  ( $n$  は整数) ご

とに周期的に存在する。ここで、 $f_s \geq 2f_B$  の場合には図 8.2 (a) に示すように隣り合う信号スペクトル同士は重ならないのに対して、 $f_s < 2f_B$  の場合には図 8.2 (b) に示すように隣り合う信号スペクトル同士が重なり正しい信号検出ができないなくなる。図 5.2 (b) のような状態をエリアシングが生じていると呼ぶ。 $f_s$  が  $2f_B$  に比べて十分大きい場合、サンプリング周波数の高速化による回路構成上の問題は生じるが、隣り合う信号スペクトル同士は十分離れるので、後のフィルタ処理が容易になり、また、後述する量子化雑音の影響を低減できる利点がある。

図 8.2 離散時間信号の時間波形とスペクトル

### 8.1.2 量子化

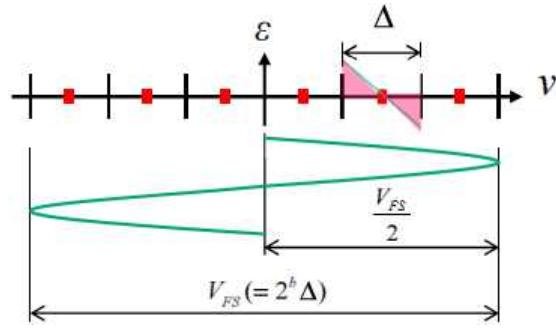

量子化は、フルスケール電圧  $V_{FS}$  を  $b$  ビットで電圧間隔（電圧ステップ幅） $\Delta$  に

分割し、各 $\Delta$ 内においてアナログ電圧値を1つの（同一の）デジタル電圧値で表わすものである。 $V_{FS}$ ,  $b$ ,  $\Delta$ の関係は次式で与えられる。

$$\Delta = \frac{V_{FS}}{2^b} \quad \rightarrow \quad V_{FS} = 2^b \Delta \quad (8.1)$$

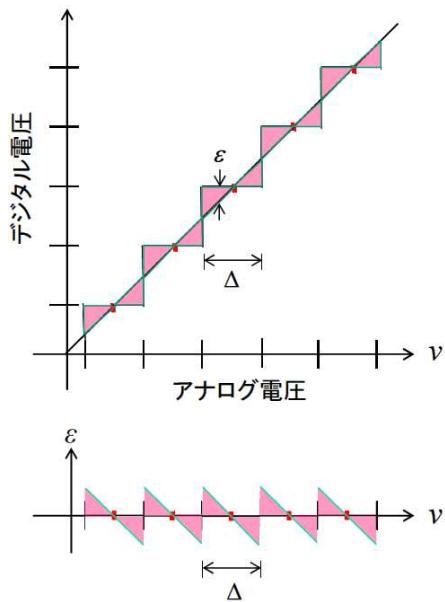

量子化により、有限の個数のデジタル電圧値にされ、これを用いて計算処理が行われる。しかし、図8.3に示す様に、量子化されたデジタル電圧の値には常に誤差 $\varepsilon$ が含まれることになる。

図8.3 量子化による誤差 $\varepsilon$

誤差 $\varepsilon$ は信号の電圧値に応じて生じるが、その生じ方はほぼランダムとなり雑音のように振る舞う。これを量子化雑音と呼ぶ。誤差 $\varepsilon$ による量子化雑音電力 $P_{Nq}$ は次式で表わせる。

$$P_{Nq} = \int_{-\Delta/2}^{\Delta/2} \frac{\varepsilon^2}{R_L} p(\varepsilon) d\varepsilon = \int_{-\Delta/2}^{\Delta/2} \varepsilon^2 \frac{1}{\Delta} d\varepsilon = \frac{\Delta^2}{12} \quad (8.2)$$

ここで、 $\Delta$ ：電圧間隔（電圧ステップ）、 $P(\varepsilon)$ ：確率密度（ $P(\varepsilon) = \frac{1}{\Delta}$ ）、 $R_L$ ：負荷抵抗（以下の検討において  $R_L = 1\Omega$  とする）

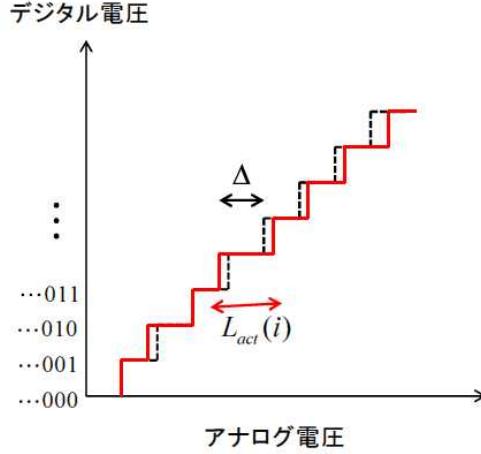

実際には、ADC/DAC の特性は、素子のばらつきやひずみなどにより理想動作からずれ、図 8.4 に示されるような特性（静特性）となる。

図 8.4 ADC/DAC の静特性

電圧間隔が理想値  $\Delta$  に対して実際の値は  $L_{act}(i)$  となり理想値からずれる。このような理想動作からのずれを以下の性能パラメータで表わす。

*DNL*:differential Non-Linearity error

$$DNL_i = \frac{L_{act}(i) - \Delta}{\Delta} \quad (8.3)$$

*INL*:Integral Non-Linearity error

$$INL_i = \sum_{j=0}^i DNL_j = \frac{\sum_{j=0}^i L_{act}(j) - (i+1)\Delta}{\Delta} \quad (8.4)$$

一方、実動作時の ADC/DAC の理想動作からのずれを表わす性能パラメータとし

て以下がある。これらはスペクトル特性を観測することにより得られる。

$$SNR_q = \frac{\text{信号電力}}{\text{量子化雑音電力}} \quad (8.5)$$

$$SFDR = \frac{\text{信号電力}}{\text{最大(3次)高調波ひずみ電力}} \quad (8.6)$$

$$SNDR = \frac{\text{信号電力}}{\text{量子化雑音電力+ひずみ電力}} \quad (8.7)$$

ここでは、ADC/DAC の量子化雑音のみによる  $SNR$  を  $SNR_q$  と表わすこととする。

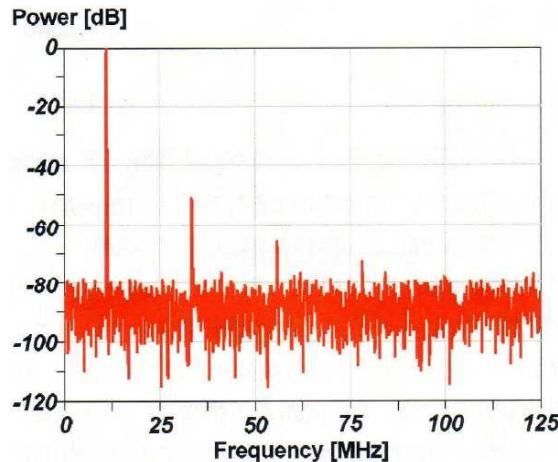

図 8.5 に周波数  $11.17MHz$  の正弦波信号を 9 ビット ADC を用い、サンプリング周波数  $250MHz$  で AD 変換した場合のスペクトル特性（シミュレーション）例を示す。スペクトル特性は ADC/DAC の動特性とも呼ばれる。ひずみにより高調波スペクトルが見られ、また、量子化雑音によるノイズフロアが見られる。

図 8.5 ADC のスペクトル特性（動特性）例

### 8.1.3 ADC/DAC の SNR

図 8.6 に、フルスケール電圧  $V_{FS}$ 、電圧振幅  $\frac{V_{FS}}{2}$  の正弦波を与えた時の電圧の様子を示す。

図 8.6 フルスケール電圧  $V_{FS}$ , 電圧振幅  $\frac{V_{FS}}{2}$  の正弦波の様子

この時, 信号電力  $P_S$  は電圧間隔  $\Delta$  に対する式 (8.1) を用いて, 次式で表わせる。

$$P_S = \frac{1}{2} \left( \frac{V_{FS}}{2} \right)^2 = \frac{1}{2} \left( \frac{2^b \Delta}{2} \right)^2 \quad (8.8)$$

一方, 量子化雑音電力  $P_{Nq}$  は式 (8.2) で与えられることから, フルスケール電圧  $V_{FS}$  で動作する正弦波の場合, 式 (8.5) で定義される  $SNR_q$  は次式で表わせる。

$$SNR_q = \frac{\text{信号電力}}{\text{量子化雑音電力}} = \frac{P_S}{P_{Nq}} = \frac{\frac{1}{2} \left( \frac{2^b \Delta}{2} \right)^2}{\frac{\Delta^2}{12}} = \frac{3}{2} 2^{2b} \quad (8.9)$$

これを dB 表示して次式が得られる。

$$SNR_q(dB) = 10 \log(SNR_q) = 10 \log \left( \frac{3}{2} 2^{2b} \right) = 6.02b + 1.76 \quad (8.10)$$

$$\rightarrow b = \frac{SNR_q(dB) - 1.76}{6.02} \quad (8.11)$$

ADC/DAC がひずみなどにより理想動作から外れる時、式 (8.7) で定義される  $SNDR$  が用いられる。この時、式 (8.11) において以下の置き換えを行う。

$$SNR_q(dB) \rightarrow SNDR(dB) \quad b \rightarrow ENOB$$

$$ENOB = \frac{SNDR(dB) - 1.76}{6.02} \quad (8.12)$$

ここで  $ENOB$  (Effective Number of Bit) は、量子化誤差とひずみに帰因する雑音を合わせた全雑音電力が、量子化雑音のみによって生じると想定（量子化雑音換算）し、その量子化雑音を生じさせる ADC/DAC のビット数といえる。

#### 8.1.4 オーバサンプリングを考慮した SNR

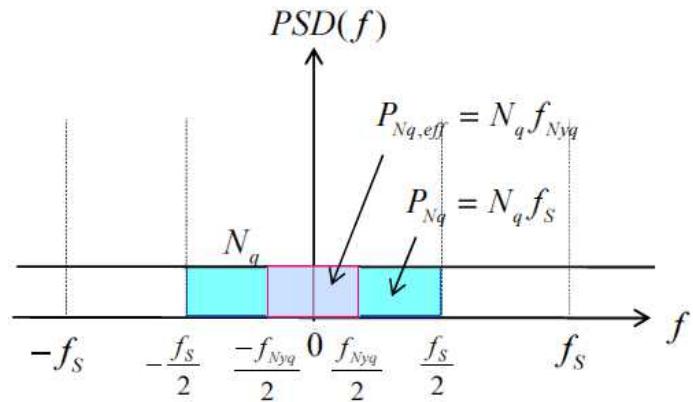

ADC/DAC の量子化雑音電力  $P_{Nq}$  の値は理想動作時に  $P_{Nq} = \frac{\Delta^2}{12}$  となる（式(8.2)）。

この値は電圧間隔  $\Delta$  によって決まるもので、サンプリング周波数  $f_s$  には依存しない。一方、雑音電力スペクトル密度  $N_q$  は次式で与えられる。

$$N_q = \frac{P_{Nq}}{f_s} = \frac{1}{12} \frac{\Delta^2}{f_s} \quad (8.13)$$

$N_q$  は、 $\Delta^2$  に比例し、 $f_s$  に反比例する関数となっている。これから、 $f_s$  を増大すると  $N_q$  の値は小さくなる。

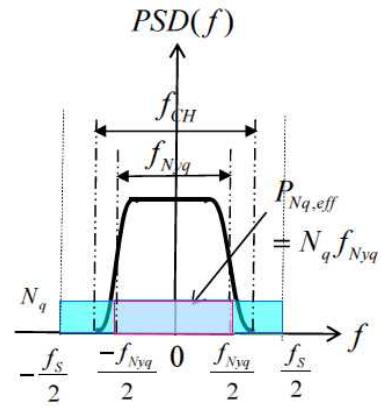

ここで、 $f_{Nyq}$  のナイキストフィルタで帯域制限した信号を考えると、信号帯域内に含まれる量子化雑音電力は等価雑音電力  $P_{Nq,eff}$  で与えられ、次式のように表わせる。

$$P_{Nq,eff} = N_q f_{Nyq} = \frac{P_{Nq}}{f_S} f_{Nyq} = \frac{P_{Nq}}{OSR} = \frac{1}{OSR} \frac{\Delta^2}{12} \quad (8.14)$$

$$OSR = \frac{f_S}{f_{Nyq}} \quad \text{オーバサンプル比} \quad (8.15)$$

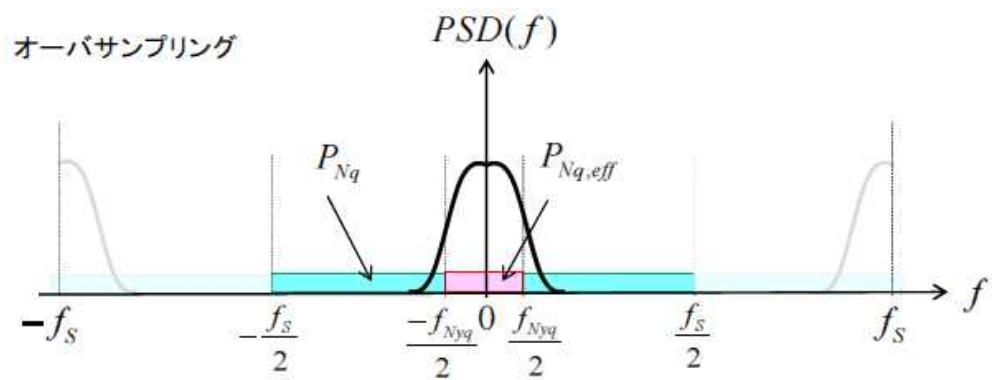

この様子を図 8.7 に示す。

(a) 量子化雑音のスペクトル

(b) ナイキストフィルタリングした信号と量子化雑音のスペクトル

図 8.7 オーバサンプル時の信号と量子化雑音スペクトル

(シングルキャリア通信の場合)

ADC/DAC が（ばらつきやひずみが無く）理想動作する時、ナイキストフィルタリングした信号と量子化雑音による  $SNR_q$  は式 (8. 14) を用いて次式で表わされる。

$$SNR_q = \frac{P_s}{P_{Nq,eff}} = OSR \frac{P_s}{P_{Nq}} \quad (8. 16)$$

さらに信号がフルスケール電圧  $V_{FS}$  で動作する正弦波の場合には、 $\frac{P_s}{P_{Nq}}$  に式 (8. 9) を用いて次式となる。

$$SNR_q = OSR \frac{3}{2} 2^{2b} \quad (8. 17)$$

上式 (8. 16), (8. 17) から、OSR を増大すると、それに比例して  $SNR_q$  も増大（改善）する。

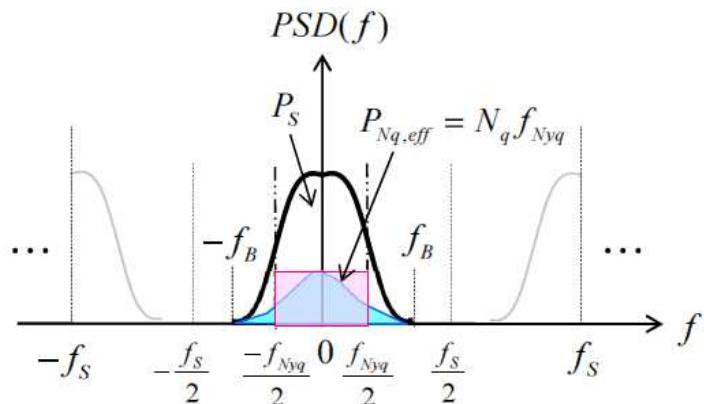

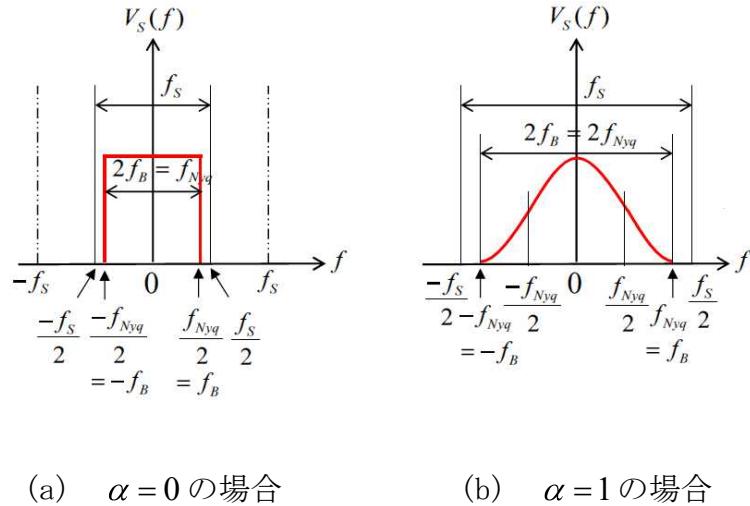

ところで、シングルキャリア通信において、ロールオフ率  $\alpha=0$  のナイキストフィルタを用いる場合、 $f_B = \frac{f_{Nyq}}{2}$  となり、これからエリアシングしないためのサンプリング周波数  $f_s$  は  $f_s \geq 2f_B = f_{Nyq}$  ( $\rightarrow OSR \geq 1$ ) とすれば良い。これに対して、 $\alpha=1$  のナイキストフィルタを用いる場合、 $f_B = f_{Nyq}$  となり、この場合は、 $f_s \geq 2f_B = 2f_{Nyq}$  ( $\rightarrow OSR \geq 2$ ) とする必要がある。この様子を図 8.8(a), (b) に示す。

図 8.8  $f_s$ ,  $f_B$ ,  $f_{Nyq}$  とオーバサンプルOSR の様子

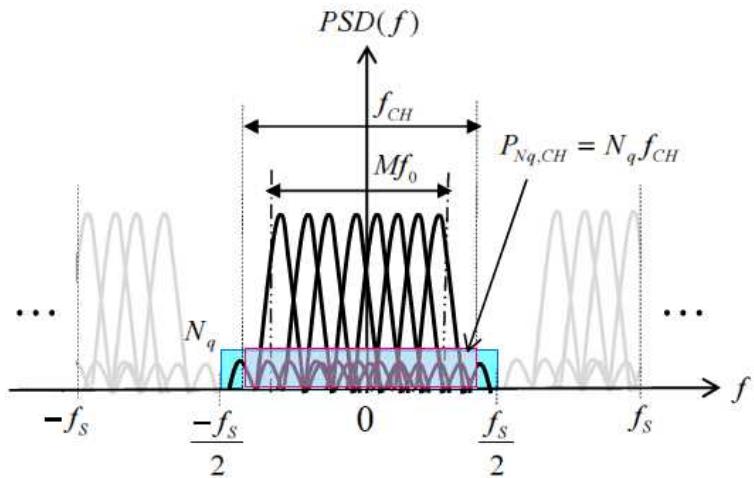

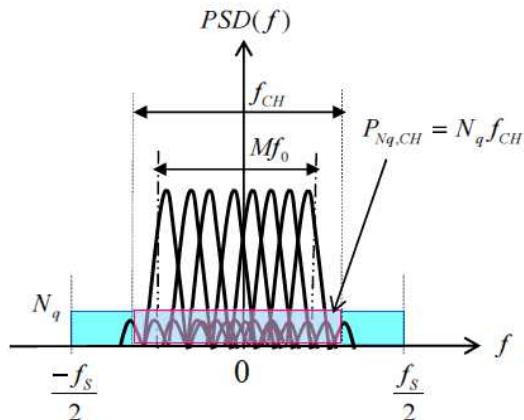

一方, 後述するマルチキャリア(OFDM)通信の場合, OSR は  $f_{CH}$  と  $f_s$  の比  $\frac{f_s}{f_{CH}}$  で与えられる (ここで,  $f_{CH} = Mf_0 + 2\Delta f_G$ ,  $f_0$  は OFDM 変調における基本周波数,  $M$  はサブキャリア数,  $\Delta f_G$  は周波数ガードバンド)。図 8.9 にマルチキャリア(OFDM)通信の場合の信号と量子化雑音スペクトルを示す。

図 8.9 オーバサンプル時の信号と量子化雑音スペクトル

(マルチキャリア (OFDM) 通信の場合)

## 8.2 シングルキャリア通信用 ADC

### 8.2.1 ADC を含む受信機構成

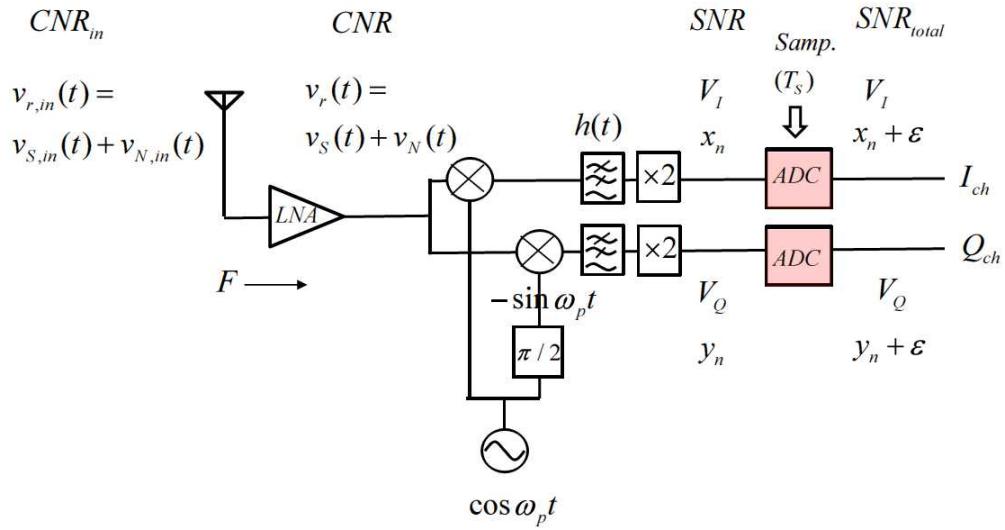

図 8.10 にシングルキャリア通信に一般的に用いられる ADC を含む受信機構成を示す。図には、各点の信号および雑音電圧も示す。

図 8.10 シングルキャリア通信に用いる受信機の構成

図において、 $v_r(t)$  は LNA で増幅後の雑音を含む搬送波電圧、 $v_s(t)$  は搬送波信号電圧、 $v_N(t)$  は搬送波周波数帯の雑音電圧であり、それぞれ次式で与えられる。

$$v_r(t) = v_s(t) + v_N(t) \quad (8.18)$$

$$\begin{aligned} v_s(t) &= A \cos(\omega_p t + \theta) \\ &= A \cos(\theta) \cos(\omega_p t) - A \sin(\theta) \sin(\omega_p t) \\ &= V_I \cos(\omega_p t) - V_Q \sin(\omega_p t) \end{aligned} \quad (8.19)$$

$$v_N(t) = x_n \cos \omega_p t - y_n \sin \omega_p t \quad (8.20)$$

ここで、

$$\langle x_n^2 \rangle = \langle y_n^2 \rangle = \sigma_n^2 \quad (8.21)$$

$\sigma_n \left( = \sqrt{\langle x_n^2 \rangle} = \sqrt{\langle y_n^2 \rangle} \right)$  は雑音電圧の実効値

$\langle \cdot \rangle$  は確率変数のアンサンブル平均値（期待値）

電圧  $v_s(t)$  の振幅  $A$  と位相  $\theta$  に信号情報がのせられる。特に *QPSK* や *QAM* のデジタル変調の場合には、ベースバンド電圧  $V_I$  と  $V_Q$  で決まる信号点に情報がのせられる。

RF 信号電圧  $v_s(t)$  は直交復調器で I, Q ベースバンドアナログ信号（電圧）  $V_I$ ,  $V_Q$  に変換され、さらに ADC でデジタル信号（電圧）に変換される。ここでは、アナログとデジタルで同一記号  $V_I$ ,  $V_Q$  を用いるが、デジタル化により量子化誤差  $\varepsilon$  による量子化雑音が発生することになる。

RF 帯雑音電圧  $v_N(t)$  も信号電圧と同様に直交復調器で I, Q ベースバンド雑音電圧  $x_n$ ,  $y_n$  に変換される。ADC では  $x_n$ ,  $y_n$  にさらに量子化誤差  $\varepsilon$  による量子化雑音が付加される。

### 8.2.2 CNR と SNR

信号電力と雑音電力の比を与える性能パラメータとして *CNR* と *SNR* があるが、これらはそれぞれ以下で定義される。

$$CNR = \frac{\text{搬送波信号電力}}{\text{搬送波雑音電力}}$$

$$SNR = \frac{\text{I, Qチャネルにおけるベースバンド信号電力}}{\text{I, Qチャネルにおけるベースバンド雑音電力}}$$

*ADC*における雑音特性を評価する場合、*ADC*が扱う信号すなわち I, Q ベースバンド信号に対する雑音特性が問題となる。このため *ADC*では評価パラメータとして *SNR* が用いられる。

一方、受信機の雑音特性には評価パラメータとして *CNR* が一般に用いられる。それでは *SNR* と *CNR* はどのような関係があるのだろうか？

ここでまず、*QPSK* や *QAM* のように I, Q チャネルを同等に用いる変調信号について検討する。

この場合、 $\langle V_I^2 \rangle = \langle V_Q^2 \rangle$  であることから、搬送波信号電圧  $v_s(t)$  による搬送波信号電力  $P_s$  は以下のように表わされる。

$$\begin{aligned} P_s &= \frac{1}{T} \int_T \langle |v_s(t)|^2 \rangle dt = \frac{\langle A^2 \rangle}{2} \\ &= \frac{1}{2} \langle V_I^2 \rangle + \frac{1}{2} \langle V_Q^2 \rangle = \langle V_I^2 \rangle = \langle V_Q^2 \rangle \end{aligned} \quad (8.22)$$

また、搬送波雑音電圧  $v_n(t)$  による搬送波雑音電力  $P_n$  は式 (8.20), (8.21) を用いて以下のように表わされる。

$$\begin{aligned} P_n &= \frac{1}{T} \int_T \langle |v_n(t)|^2 \rangle dt \\ &= \frac{1}{2} \langle x_n^2 \rangle + \frac{1}{2} \langle y_n^2 \rangle = \langle x_n^2 \rangle = \langle y_n^2 \rangle = \sigma_n^2 \end{aligned} \quad (8.23)$$

式 (8.22), (8.23) から *CNR* は以下で与えられる。

$$CNR = \frac{P_s}{P_n} = \frac{\langle A \rangle^2 / 2}{\sigma_n^2} = \frac{\langle V_I^2 \rangle}{\sigma_n^2} = \frac{\langle V_Q^2 \rangle}{\sigma_n^2} \quad (8.24)$$

一方、ベースバンド信号電力とベースバンド雑音電力の比で定義される *SNR* は I チャネルの場合と Q チャネルの場合で等しく以下で与えられる。

$$SNR = \frac{\langle V_I^2 \rangle}{\langle x_n^2 \rangle} = \frac{\langle V_Q^2 \rangle}{\langle y_n^2 \rangle} = \frac{\langle V_I^2 \rangle}{\sigma_n^2} = \frac{\langle V_Q^2 \rangle}{\sigma_n^2} \quad (8.25)$$

式 (8.24) と (8.25) の比較から, *QPSK* や *QAM* 等の I, Q チャネルを同等に用いる変調信号では次式が成り立つ。

$$CNR = SNR \quad (8.26)$$

次に, I, Q チャネルを同等に用いない *BPSK* 変調信号について考える。 *BPSK* の場合, 式(8.19)において常に  $V_Q = 0$  となっている。これから *BPSK* 変調信号の場合, 搬送波信号電力  $P_s$  は以下のように表わされる。

$$P_s = \frac{1}{2} \langle A^2 \rangle = \frac{1}{2} \langle V_I^2 \rangle \quad (8.27)$$

一方, 搬送波雑音電圧  $v_N(t)$  による搬送波雑音電力  $P_N$  は *QPSK* や *QAM* の場合と等しく, 式 (8.23) で与えられる。これから, *BPSK* の場合,  $CNR_{BPSK}$  は以下で表わされる。

$$CNR_{BPSK} = \frac{P_s}{P_N} = \frac{\langle A \rangle^2 / 2}{\sigma_n^2} = \frac{\langle V_I^2 \rangle / 2}{\sigma_n^2} \quad (8.28)$$

一方, ベースバンド信号電力とベースバンド雑音電力の比で定義される  $SNR_{BPSK}$  は I チャネルにのみ存在し以下で与えられる。

$$SNR_{BPSK} = \frac{\langle V_I^2 \rangle}{\langle x_n^2 \rangle} = \frac{\langle V_I^2 \rangle}{\sigma_n^2} \quad (8.29)$$

式 (8.28) と (8.29) の比較から,  $BPSK$  では,  $CNR_{BPSK}$  と  $SNR_{BPSK}$  の間に次式が成り立つ。

$$CNR_{BPSK} = \frac{1}{2} SNR_{BPSK} \quad (8.30)$$

以上の結果をまとめると, I, Q チャネルを同等に用いる変調方式であれば  $CNR = SNR$  が成り立つ。このような場合として,  $QPSK$ ,  $QAM$  変調があるが, 後述する  $OFDM$  変調も I, Q チャネルを同等に用いることから, この関係が成り立つ。これに対し, 一方のベースバンドチャネル (I チャネル) のみを使う  $BPSK$  変調では  $CNR_{BPSK} = \frac{1}{2} SNR_{BPSK}$  となる。

### 8.2.3 ピークファクタ par と PAPR

$ADC$  では与えられたフルスケール電圧  $V_{FS}$  を超えない範囲で信号電圧が最大となるようにすることにより量子化雑音の影響を最小化できる。このため  $ADC$  ではベースバンド信号電圧のピーク値  $V_{peak}$  がフルスケール電圧  $V_{FS}$  に対して  $\frac{V_{FS}}{2} \geq V_{peak} (>0)$  となるように設計する必要がある。 $ADC$  の設計のため, ベースバンド信号電圧 (期待値)  $\sqrt{\langle V_I^2 \rangle}$ ,  $\sqrt{\langle V_Q^2 \rangle}$  と  $\frac{V_{FS}}{2} (\geq V_{peak} > 0)$  を関係付ける次式で与えられるピークファクタ  $par$  を導入する。

$$\begin{aligned} par &= \left( \frac{\text{フルスケール電圧} \div 2}{\text{ベースバンド信号電圧の期待値}} \right)^2 \\ &= \left( \frac{V_{FS}/2}{\sqrt{\langle V_I^2 \rangle}} \right)^2 = \left( \frac{V_{FS}/2}{\sqrt{\langle V_Q^2 \rangle}} \right)^2 \end{aligned} \quad (8.31)$$

一方, RF 信号に対するピークファクタとして次式で定義される  $PAPR$  (Peak to Average Power Ratio, クレストファクタとも呼ばれる) がある。

$$PAPR = \frac{\text{搬送波RF信号の最大瞬時電力 (ピーク電力)}}{\text{搬送波RF信号の平均電力}} = \frac{P_{S,peak}}{P_{S,avr}} \quad (8.32)$$

*ADC* の *par* は各変調信号に対して、どのように与えられるのであろうか？また、*par* と *PAPR* にはどのような関係があるのであろうか？

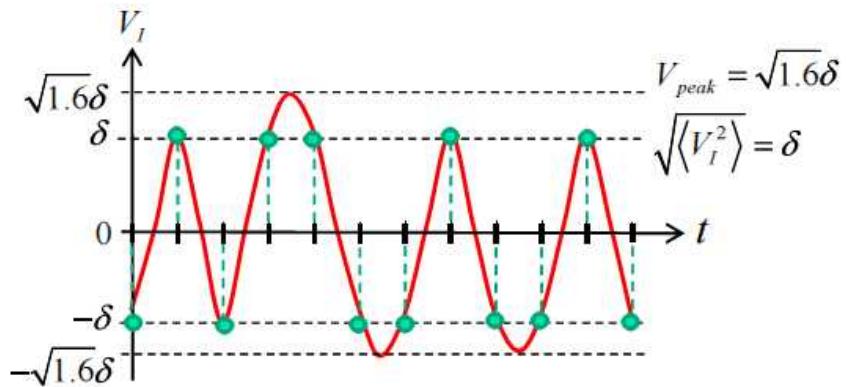

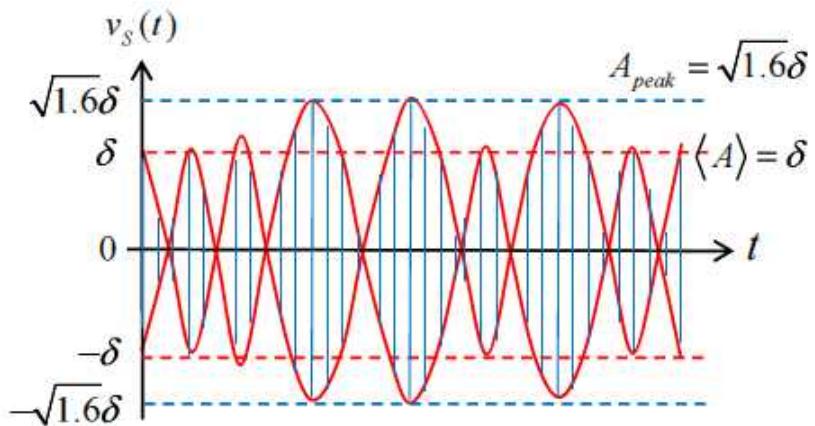

まず、*BPSK* の場合について述べる。一般にナイキストフィルタにより帯域制限された *BPSK* 変調信号では、ベースバンド信号電圧  $V_I$  の時間波形が図 8.11 のようになる。 $V_I$  の期待値は  $\sqrt{\langle V_I^2 \rangle} = \delta$  となるが、フィルタの存在により、電圧は変動する特性となる。この時、最大（ピーク）電圧値  $V_{peak}$  は概略以下となる。

$$V_{peak} \approx \sqrt{1.6} \sqrt{\langle V_I^2 \rangle} = \sqrt{1.6}\delta \quad (8.33)$$

上式 (8.33) の関係は、同一の  $V_I$  の値が連續して続く場合に生じ、 $\sin c$  関数で表わされた隣り合うパルスどうしの足し算を考えると妥当なものといえる。

図 8.11 ナイキストフィルタにより帯域制限された *BPSK* 変調信号のベースバンド電圧の時間波形の様子

図から  $BPSK$  の場合、 $ADC$  のフルスケール電圧は  $V_{FS} / 2 = V_{peak}$  とすればよいといえ、これから、ベースバンド信号電圧に対するピークファクタ  $par$  は以下で与えられる。

$$par = \left( \frac{V_{FS} / 2}{\sqrt{\langle V_I^2 \rangle}} \right)^2 = \left( \frac{\sqrt{1.6}\delta}{\delta} \right)^2 = 1.6 \quad (8.34)$$

図 8.12 に、図 8.11 のベースバンド信号に対応した RF 信号の電圧波形を示す。

図 8.12 ナイキストフィルタにより帯域制限された  $BPSK$  変調信号の搬送波 RF 信号の電圧波形の様子

図において  $\langle A \rangle$  は RF 信号の電圧振幅のアンサンブル平均値（期待値）、 $A_{peak}$  はピーク電圧振幅であり、ベースバンド信号電圧と以下の関係にある。

$$\left. \begin{aligned} \langle A \rangle &= \sqrt{\langle V_I^2 \rangle} = \delta \\ \frac{V_{FS}}{2} &= A_{peak} = V_{peak} = \sqrt{1.6} \sqrt{\langle V_I^2 \rangle} = \sqrt{1.6}\delta \end{aligned} \right\} \quad (8.35)$$

これから、RF 信号に対する  $PAPR$  は以下で与えられる。

$$PAPR = \frac{P_{S,peak}}{P_{S,avr}} = \frac{A_{peak}^2 / 2}{\langle A \rangle^2 / 2} = \frac{V_{peak}^2 / 2}{\langle V_I^2 \rangle / 2} = \frac{1.6\delta^2 / 2}{\delta^2 / 2} = 1.6 \quad (8.36)$$

式 (8.34) と (8.36) の比較から, *BPSK* の場合には  $par = PAPR = 1.6$  となっている。

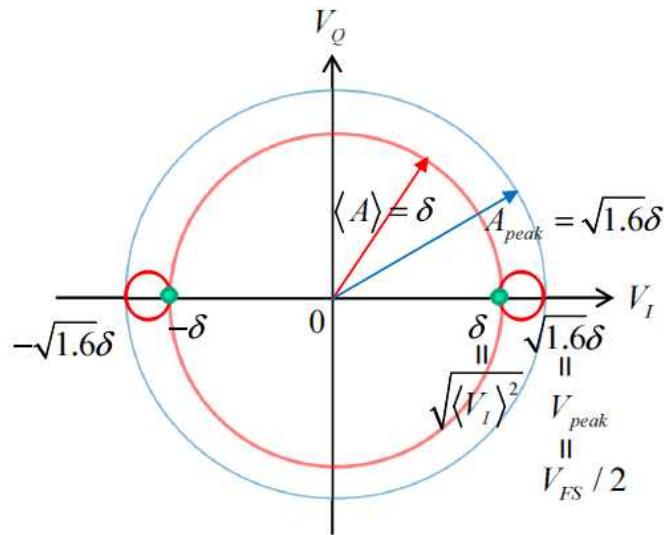

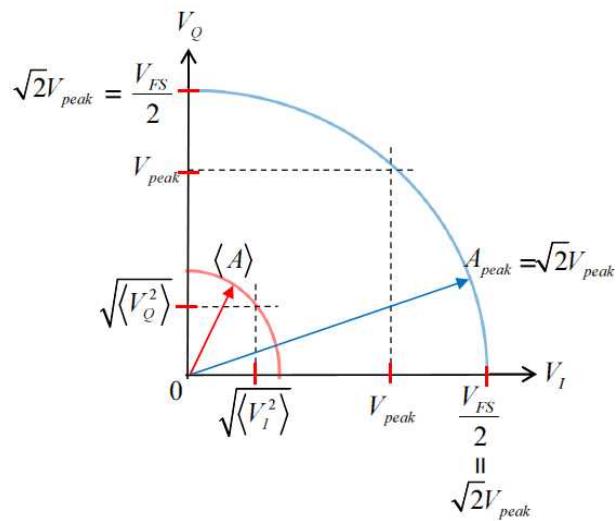

図 8.13 にナイキストフィルタにより帯域制限された *BPSK* 変調信号の信号点配置図 (Constellation diagram) (信号空間ダイアグラムとも呼ばれる) を示す。

図 8.13 ナイキストフィルタにより帯域制限された *BPSK* 変調信号の信号点配置図

図には, RF 信号の平均電圧の軌跡とフィルタによるピーク電圧発生の様子も示している (図の赤線で示した大円と小円)。また, RF 信号の  $\langle A \rangle$ ,  $A_{peak}$ , ベースバンド信号の  $\sqrt{\langle V_I^2 \rangle}$ ,  $V_{peak}$ ,  $V_{FS} / 2$  の関係も示している。図のサンプリング点の  $V_I$  成分が  $V_I$  の時間波形を与える。

図 8.13 には, 図 8.11 と図 8.12 で得られた情報がすべて含まれている。これから, 以下の *QPSK*, *QAM* の解析は信号点配置図のみを用いて行う。

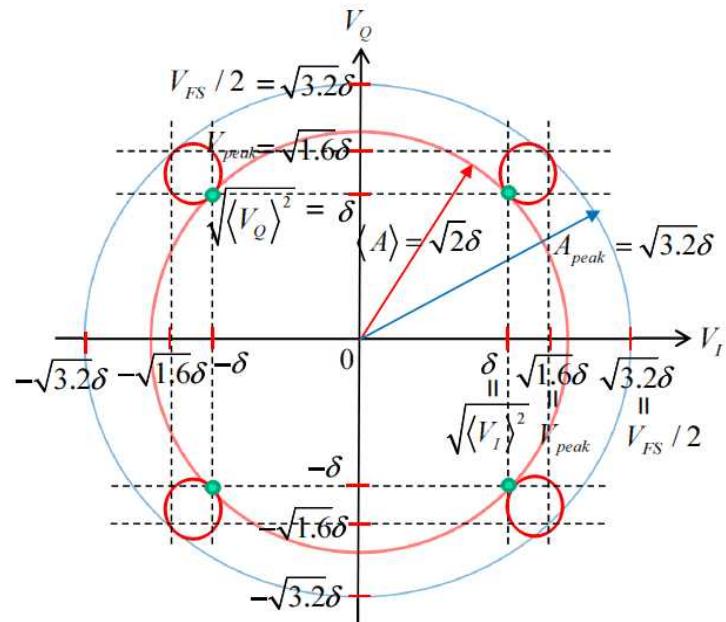

次に, *QPSK* の場合について述べる。図 8.14 にナイキストフィルタにより帶

域制限された *QPSK* 変調信号の信号点配置図を示す。図には、RF 信号の平均電圧の軌跡とフィルタによるピーク電圧発生の様子も示している（図の赤線で示した大円と小円）。ピーク電圧発生は *BPSK* と同様に、 $V_I$ ,  $V_Q$  それぞれにおいて同一の  $V_I$ ,  $V_Q$  の値が連続して続く場合に生じる。図には、RF 信号の  $\langle A \rangle$ ,  $A_{peak}$ , ベースバンド信号の  $\sqrt{\langle V_I^2 \rangle}$ ,  $\sqrt{\langle V_Q^2 \rangle}$ ,  $V_{peak}$ ,  $V_{FS}/2$  の関係も示している。*QPSK* の場合、これらの電圧値には以下の関係がある。

$$\left. \begin{aligned} \frac{\langle A \rangle}{\sqrt{2}} &= \sqrt{\langle V_I^2 \rangle} = \sqrt{\langle V_Q^2 \rangle} = \delta \\ \frac{V_{FS}}{2} &= A_{peak} = \sqrt{2}V_{peak} = \sqrt{2} \times \sqrt{1.6}\delta = \sqrt{3.2}\delta \end{aligned} \right\} \quad (8.37)$$

図 8.14 ナイキストフィルタにより帯域制限された *QPSK* 変調信号の信号点配置図

*QPSK* の場合には、信号検出の途中段階で  $V_I$ ,  $V_Q$  の座標が  $45^\circ$  傾いている場

合にも対応出来るようにするため、上式 (8.37) の 2 行目のように

$$\frac{V_{FS}}{2} = A_{peak} = \sqrt{2}V_{peak} \text{ としている (BPSK の場合には } \frac{V_{FS}}{2} = A_{peak} = V_{peak} \text{ )。}$$

これから、RF 帯信号に対する PAPR およびベースバンド信号に対する par は以下で与えられる。

$$PAPR = \frac{P_{S,peak}}{P_{S,avr}} = \frac{A_{peak}^2 / 2}{\langle A \rangle^2 / 2} = \frac{3.2\delta^2 / 2}{\delta^2} = 1.6 \quad (8.38)$$

$$par = \left( \frac{V_{FS} / 2}{\sqrt{\langle V_I \rangle^2}} \right)^2 = \left( \frac{V_{FS} / 2}{\sqrt{\langle V_Q \rangle^2}} \right)^2 = \left( \frac{\sqrt{3.2}\delta}{\delta} \right)^2 = 3.2 \quad (8.39)$$

式 (8.38), (8.39) から  $par = 2 \times PAPR$  となっている (BPSK の場合には  $par = PAPR$  )。

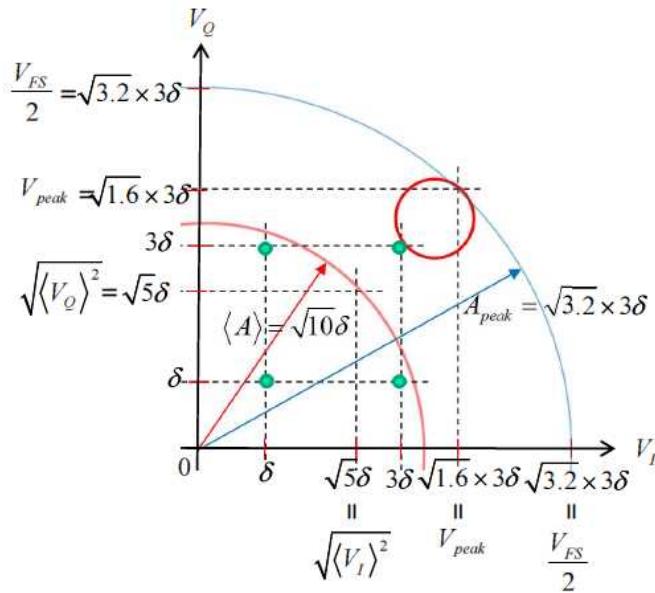

さらに次に、16QAM の場合について述べる。図 8.15 にナイキストフィルタにより帯域制限された 16QAM 変調信号の信号点配置図を示す。なお、図では  $V_I$ ,  $V_Q$  座標の第 1 象限のみを示している (他の象限も同じ)。

図には、RF 信号の平均電圧の軌跡とフィルタによるピーク電圧発生の様子も示している (図の赤線で示した大円と小円)。

ピーク電圧発生は最も外側にある信号点  $(V_I, V_Q) = (3\delta, 3\delta)$  が連続して続く場合に生じる。図には、RF 信号の電圧振幅の期待値  $\langle A \rangle$ , ピーク振幅  $A_{peak}$ , ベースバンド信号の  $\sqrt{\langle V_I^2 \rangle}$ ,  $\sqrt{\langle V_Q^2 \rangle}$ ,  $V_{peak}$ ,  $V_{FS} / 2$  の関係も示している。16QAM の場合、これらの電圧値には以下の関係がある。

$$\left. \begin{aligned} \frac{\langle A \rangle}{\sqrt{2}} &= \sqrt{\langle V_I^2 \rangle} = \sqrt{\langle V_Q^2 \rangle} = \sqrt{5}\delta \\ \frac{V_{FS}}{2} &= A_{peak} = \sqrt{2}V_{peak} = \sqrt{2} \times \sqrt{1.6} \times 3\delta = \sqrt{3.2} \times 3\delta \end{aligned} \right\} \quad (8.40)$$

図 8.15 ナイキストフィルタにより帯域制限された16QAM 変調信号の

信号点配置図（第1象限）

16QAM の場合にも、信号検出の途中段階で  $V_I$ ,  $V_Q$  の座標が  $45^\circ$  傾いている場合にも対応出来るようにするため、上式の 2 行目のように  $\frac{V_{FS}}{2} = A_{peak} = \sqrt{2}V_{peak}$  と

している。これから、RF 信号に対する PAPR およびベースバンド信号に対する

par は以下で与えられる。

$$PAPR = \frac{P_{S,peak}}{P_{S,avr}} = \frac{A_{peak}^2 / 2}{\langle A \rangle^2 / 2} = \frac{28.8\delta^2 / 2}{5\delta^2} = 2.9 \quad (8.41)$$

$$par = \left( \frac{V_{FS}/2}{\sqrt{\langle V_I^2 \rangle}} \right)^2 = \left( \frac{V_{FS}/2}{\sqrt{\langle V_Q^2 \rangle}} \right)^2 = \left( \frac{\sqrt{3.2} \times 3\delta}{\sqrt{5}\delta} \right)^2 = 5.8 \quad (8.42)$$

式 (8.41), (8.42) から  $par = 2 \times PAPR$  となっている。

以上の議論から,  $BPSK$  変調では搬送波 RF 信号において一般的に用いられる  $PAPR$  が ADC の  $par$  としてそのまま用いられる。これに対して, I, Q チャネルを同等に用いる  $QPSK$  や  $QAM$  および後述の  $OFDM$  変調では  $2 \times PAPR$  が  $par$  として用いられる。

#### 8.2.4 ADC による $CNR_{total}$ の劣化率 $\gamma$ と ADC のビット数 $b$

量子化雑音を考慮した場合の ADC 出力端における信号対雑音電力比  $SNR_{total}$  を考える。 $QPSK$  と  $QAM$  では I チャネルと Q チャネルは同等である。一方,  $BPSK$  では信号が存在するのは I チャネルである。このことから, ここでは I チャネルについて定式化する。この時  $SNR_{total}$  は次式で表わせる。

$$\begin{aligned} SNR_{total} &= \frac{\langle V_I^2 \rangle}{\langle x_n^2 \rangle + P_{Nq,eff}} = \frac{1}{\frac{\langle x_n^2 \rangle}{\langle V_I^2 \rangle} + \frac{P_{Nq,eff}}{\langle V_I^2 \rangle}} \\ &= \frac{1}{\frac{1}{SNR} + \frac{1}{OSR} \frac{\Delta^2}{12} \frac{par}{(V_{FS}/2)^2}} = \frac{1}{\frac{1}{SNR} + \frac{1}{3} \frac{1}{OSR} \frac{par}{2^{2b}}} \end{aligned} \quad (8.43)$$

ここで,  $P_{Nq,eff}$  はナイキストフィルタによる帯域制限を受けた量子化雑音電力である。式変形には以下の関係を用いている。

$$SNR = \frac{\langle V_I^2 \rangle}{\langle x_n^2 \rangle} \quad (8.44) \quad (\text{式 (8.25) と同じ})$$

$$P_{Nq,eff} = \frac{P_{Nq}}{OSR} = \frac{1}{OSR} \frac{\Delta^2}{12} \quad (8.45) \text{ (式 (8.14) と同じ)}$$

$$par = \left( \frac{V_{FS}/2}{\sqrt{\langle V_I^2 \rangle}} \right)^2 \quad (8.46) \text{ (式 (8.31) と同じ)}$$

$$V_{FS} = 2^b \Delta \quad (8.47) \text{ (式 (8.1) と同じ)}$$

BPSK では,  $CNR = \frac{1}{2} SNR$  であることから, 式(8.43)において  $SNR \rightarrow 2CNR$ ,

$SNR_{total} \rightarrow 2CNR_{total}$  と置き換えることにより次式が得られる。

$$CNR_{total} = \frac{1}{2} \frac{1}{\frac{1}{2CNR} + \frac{1}{3} \frac{1}{OSR} \frac{1}{2^{2b}} par} = \frac{1}{\frac{F}{CNR_{in}} + \frac{2}{3} \frac{1}{OSR} \frac{1}{2^{2b}} par} \quad (8.48)$$

$CNR_{in}$  は受信機入力端での  $CNR$ ,  $F$  は雑音指數

ここで, 量子化雑音を無視できる場合 ( $b \rightarrow \infty$ ,  $\Delta \rightarrow 0$ ) の  $CNR_{total,0}$  は,

$$CNR_{total,0} = \frac{CNR_{in}}{F} \quad (8.49)$$

これから, ADC による量子化雑音が存在することによる  $CNR_{total}$  の  $CNR_{total,0}$  にたいする劣化率  $\gamma$  は以下となる。

$$\gamma = \frac{CNR_{total}}{CNR_{total,0}} = \frac{1}{1 + \frac{2}{3} \frac{1}{OSR} \frac{1}{2^{2b}} \frac{par}{F} \frac{CNR_{in}}{F}} \quad (8.50)$$

上式 (8.50) を  $b$  について解くことにより, BPSK の場合のビット数  $b$  が以下のようになれる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{2}{3} \frac{\text{par} \cdot \text{CNR}_{in}}{\text{OSR} \cdot F} \frac{\gamma}{1-\gamma} \right) \quad (8.51)$$

一方, *QPSK* および *QAM* では,  $\text{CNR} = \text{SNR}$  であることから, 式 (8.43)において  $\text{SNR} \rightarrow \text{CNR}$ ,  $\text{SNR}_{total} \rightarrow \text{CNR}_{total}$  と置き換えることにより次式が得られる。

$$\text{CNR}_{total} = \frac{1}{\frac{1}{\text{CNR}} + \frac{1}{3} \frac{1}{\text{OSR}} \frac{\text{par}}{2^{2b}}} = \frac{1}{\frac{F}{\text{CNR}_{in}} + \frac{1}{3} \frac{1}{\text{OSR}} \frac{\text{par}}{2^{2b}}} \quad (8.52)$$

これから, ADC による量子化雑音が存在することによる  $\text{CNR}_{total}$  の  $\text{CNR}_{total,0}$  にたいする劣化率  $\gamma$  は以下となる。

$$\gamma = \frac{\text{CNR}_{total}}{\text{CNR}_{total,0}} = \frac{1}{1 + \frac{1}{3} \frac{1}{\text{OSR}} \frac{\text{par}}{2^{2b}} \frac{\text{CNR}_{in}}{F}} \quad (8.53)$$

上式 (8.53) を  $b$  について解くことにより, I, Q チャネルを同等に用いる *QPSK*, *QAM* の場合のビット数  $b$  が以下のように得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{1}{3} \frac{\text{par} \cdot \text{CNR}_{in}}{\text{OSR} \cdot F} \frac{\gamma}{1-\gamma} \right) \quad (8.54)$$

ここで得られた  $\text{CNR}_{total}$  を用いて ADC 量子化雑音を考慮した受信機のビット誤り率  $BER$  を求めることができる。ここで, *QPSK*, *QAM* のビット数  $b$  は同じ式 (8.54) で与えられる。*QPSK*, *QAM* の違いはピークファクタ  $par$  の値にのみあらわれる。これに対し, *BPSK* のビット数  $b$  は式 (8.51) であたえられ, *QPSK*, *QAM* の場合と式の形が異なっている。

### 8.3 マルチキャリア (OFDM) 通信用 ADC

マルチキャリア (*OFDM*) 通信に一般的に用いられる受信機構成は ADC の部分まではシングルキャリア通信の場合の図 8.10 と同じ構成である。

I, Q チャネルを同等に用いるマルチキャリア（OFDM）変調信号では  $CNR$  と  $SNR$  の関係がシングルキャリア  $QPSK$  や  $QAM$  の変調信号の場合と同様になり、次式の関係がある。

$$CNR = SNR \quad (8.55) \text{ (式 (8.26) と同じ)}$$

次にマルチキャリア（OFDM）変調信号のピークファクタ  $par$  と  $PAPR$  について述べる。

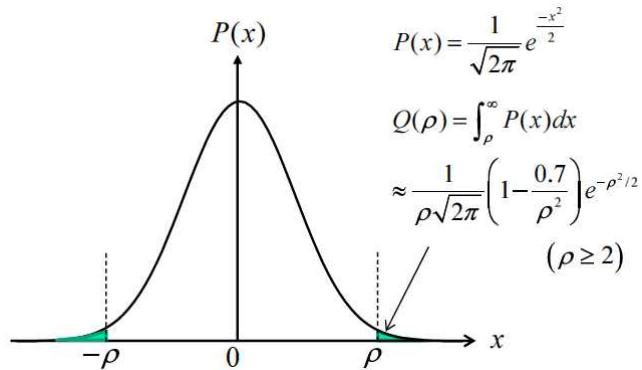

マルチキャリア（OFDM）変調信号において、サブキャリア数  $M$  が増大すると、信号の電圧振幅の分布は熱雑音と同様（ガウス分布）になると考えられる。図 8.16 に標準偏差  $\sigma = 1$  のガウス分布を示す。図において、例えば確率変数  $x$  が、

$|x| \geq \rho = 3.5$  となる確率  $P$  は  $P = 2Q(\rho) = 2Q(3.5) \approx 4.7 \times 10^{-4}$  となる。

図 8.16 ガウス分布  $P(x)$  と補関数  $Q(\rho)$

ガウス分布に従う OFDM 変調信号において、ベースバンド信号  $V_I$  の電圧振幅が  $3.5\sqrt{\langle V_I^2 \rangle} (= V_{peak})$  以上となる確率は  $P_I \approx 4.7 \times 10^{-4}$  となる。Q チャネルも同様にベースバンド信号  $V_Q$  の電圧振幅が  $3.5\sqrt{\langle V_Q^2 \rangle} (= V_{peak})$  以上となる確率は  $P_Q \approx 4.7 \times 10^{-4}$  となる。これから、 $V_I$ ,  $V_Q$  が同時に  $V_{peak}$  以上となる確率は  $P_{total} = P_I P_Q \approx 2.2 \times 10^{-9}$  となる。 $V_I$ ,  $V_Q$  が同時に  $V_{peak} = 3.5\sqrt{\langle V_I^2 \rangle} = 3.5\sqrt{\langle V_Q^2 \rangle}$  以上

となる部分、すなわち、RF信号の振幅が  $A_{peak} = \sqrt{2}V_{peak}$  以上となる部分をピークカットして用いるものとする。この時、OFDM変調信号のピーク電圧振幅は  $A_{peak} = \sqrt{2}V_{peak}$  であるといえる。

図8.17にOFDM変調信号の信号空間ダイアグラムを示す。図では  $V_I$ ,  $V_Q$  座標の第1象限のみを示している（他の象限も同じ）。

図8.17 OFDM変調の信号空間ダイアグラム

図には、RF信号の電圧振幅の期待値  $\langle A \rangle$  とピーク電圧  $A_{peak}$ 、ベースバンド信号電圧の期待値  $\sqrt{\langle V_I^2 \rangle}$ ,  $\sqrt{\langle V_Q^2 \rangle}$ , ピーク電圧  $V_{peak}$ , ADCのフルスケール電圧  $V_{FS}$  の関係を示す。これらの電圧値には以下の関係がある。

$$\left. \begin{aligned} \frac{\langle A \rangle}{\sqrt{2}} &= \sqrt{\langle V_I^2 \rangle} = \sqrt{\langle V_Q^2 \rangle} \\ \frac{V_{FS}}{2} &= A_{peak} = \sqrt{2}V_{peak} = \sqrt{2} \times 3.5\sqrt{\langle V_I^2 \rangle} \end{aligned} \right\} \quad (8.55)$$

上式の 2 行目は、信号検出の途中段階で  $V_I$ ,  $V_Q$  の座標が  $45^\circ$  傾いている場合にも対応出来るようにするものである。 $V_{peak} = 3.5\sqrt{\langle V_I^2 \rangle} = 3.5\sqrt{\langle V_Q^2 \rangle}$  とすると、RF 信号に対する PAPR およびベースバンド信号に対する par は以下で与えられる。なお、I チャネルと Q チャネルは同等であることから、式の導出は I チャネルについてのみ行っている。

$$PAPR = \frac{P_{S,peak}}{P_{S,avr}} = \frac{A_{peak}^2 / 2}{\langle A \rangle^2 / 2} = \frac{3.5^2 \langle V_I^2 \rangle}{\langle V_I^2 \rangle} = 3.5^2 \quad (8.56)$$

$$par = \left( \frac{V_{FS} / 2}{\sqrt{\langle V_I^2 \rangle}} \right)^2 = \left( \frac{\sqrt{2} \times 3.5 \sqrt{\langle V_I^2 \rangle}}{\sqrt{\langle V_I^2 \rangle}} \right)^2 = 2 \times 3.5^2 \quad (8.57)$$

式 (8.56), (8.57) から  $par = 2 \times PAPR$  となっている。

次に、量子化雑音を考慮した場合の ADC 出力端における信号対雑音電力比  $SNR_{total}$  を考える。OFDM では I チャネルと Q チャネルは同等であるので、ここでは I チャネルについて定式化する。この時  $SNR_{total}$  は次式で表わせる。

$$\begin{aligned} SNR_{total} &= \frac{\langle V_I^2 \rangle}{\langle x_n^2 \rangle + P_{Nq,eff}} = \frac{1}{\frac{\langle x_n^2 \rangle}{\langle V_I^2 \rangle} + \frac{P_{Nq,eff}}{\langle V_I^2 \rangle}} = \frac{1}{\frac{1}{SNR} + \frac{P_{Nq}}{OSR} \frac{1}{\langle V_I^2 \rangle}} \\ &= \frac{1}{\frac{1}{SNR} + \frac{1}{OSR} \frac{\Delta^2}{12} \frac{par}{(V_{FS} / 2)^2}} = \frac{1}{\frac{1}{SNR} + \frac{1}{3} \frac{1}{OSR} \frac{par}{2^{2b}}} \end{aligned} \quad (8.58)$$

ここで、OFDM 変調の OSR は次式で与えられる（図 8.9 参照）

$$OSR = \frac{f_s}{f_{CH}} \quad (8.59)$$

$f_s$  : サンプリング周波数,

$$f_{CH} : OFDM \text{ 変調信号のチャネル帯域幅}$$

*OFDM* では,  $CNR = SNR$  であることから, 式 (8. 58) において  $SNR \rightarrow CNR$ ,  $SNR_{total} \rightarrow CNR_{total}$  と置き換えることにより次式が得られる。

$$CNR_{total} = \frac{1}{\frac{1}{CNR} + \frac{1}{3} \frac{1}{OSR} \frac{1}{2^{2b}} par} = \frac{1}{\frac{F}{CNR_{in}} + \frac{1}{3} \frac{1}{OSR} \frac{1}{2^{2b}} par} \quad (8. 60)$$

ここで, 量子化雑音を無視できる場合 ( $b \rightarrow \infty, \Delta \rightarrow 0$ ) の  $CNR_{total,0}$  に対する劣化率  $\gamma$  は以下となる。

$$\gamma = \frac{CNR_{total}}{CNR_{total,0}} = \frac{1}{1 + \frac{1}{3} \frac{1}{OSR} \frac{par}{2^{2b}} \frac{CNR_{in}}{F}} \quad (8. 61)$$

上式 (8. 61) を  $b$  について解くことにより, *OFDM* の場合のビット数  $b$  が以下のように得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{1}{3} \frac{par \cdot CNR_{in}}{OSR \cdot F} \frac{\gamma}{1-\gamma} \right) \quad (8. 62)$$

これまで述べた変調方式の違いによる  $CNR_{total}$ ,  $\gamma$ , および  $b$  の設計式を, オーバサンプル比  $OSR$  の式およびピークファクタ  $par$  の値とともに, 表 8. 1 にまとめて示す。なお, 表にはシングルキャリア  $64QAM$  および  $256QAM$  の場合についても示している。

以上の議論において, ADC は理想動作し, 雜音は量子化雑音のみによるとしてきた。しかし, 実際には, ひずみ等により生じる雑音が付加され, これを考慮する必要がある。これを行うためには, ここで定式化したビット数  $b$  を式 (8. 12) で導入した  $ENOB$  に置き換えて考えれば良い。

表 8.1 ADC を含む受信機の  $CNR_{total}$ ,  $\gamma$ ,  $b$  の設計式まとめ

| 通信方式    | 変調   | $CNR_{total}$                                                       | $\gamma$                                                                        | $b$                                                                                                                 | $OSR$                                                                                                               | $par$              | $PAPR$                           |

|---------|------|---------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------|

|         |      |                                                                     |                                                                                 |                                                                                                                     |                                                                                                                     |                    |                                  |

| BPSK    |      | $\frac{1}{CNR_{in}} + \frac{2}{3} \frac{1}{OSR} \frac{par}{2^{2b}}$ | $\frac{1}{1 + \frac{2}{3} \frac{1}{OSR} \frac{par}{2^{2b}}} \frac{CNR_{in}}{F}$ | $\frac{1}{2 \log 2} \log \left( \frac{2}{3} \frac{par \cdot CNR_{in}}{OSR \cdot F} \frac{\gamma}{1-\gamma} \right)$ |                                                                                                                     | 1.6<br>(2.0dB)     | 1.6<br>(2.0dB)                   |

| QPSK    |      |                                                                     |                                                                                 |                                                                                                                     | $\frac{f_s}{f_{Nyq}}$                                                                                               | 2×1.6<br>2×2.9     | 1.6<br>(2.0dB)<br>2.9<br>(4.6dB) |

| 16QAM   |      |                                                                     |                                                                                 |                                                                                                                     |                                                                                                                     | 2×3.7              | 3.7<br>(5.7dB)                   |

| 64QAM   |      |                                                                     |                                                                                 | $\frac{1}{1 + \frac{1}{3} \frac{1}{OSR} \frac{par}{2^{2b}}} \frac{CNR_{in}}{F}$                                     | $\frac{1}{2 \log 2} \log \left( \frac{1}{3} \frac{par \cdot CNR_{in}}{OSR \cdot F} \frac{\gamma}{1-\gamma} \right)$ | 2×4.2              | 4.2<br>(6.2dB)                   |

| 256QAM  |      |                                                                     |                                                                                 |                                                                                                                     |                                                                                                                     |                    |                                  |

| マルチキャリア | OFDM |                                                                     |                                                                                 |                                                                                                                     | $\frac{f_s}{f_{CH}}$                                                                                                | 2×3.5 <sup>2</sup> | 3.5 <sup>2</sup><br>(10.9dB)     |

## 8.4 通信用 ADC の仕様設計例

### 8.4.1 60GHz 帯シングルキャリア通信用 ADC

シングルキャリア通信の例として、 IEEE802.15.3c 対応 60GHz 帯 WPAN (Wireless Personal Area Network) システム<sup>[7]</sup>を取り上げ、その受信機に用いられる ADC の仕様について検討する。図 8.18 に受信機に対する要求性能（の一部）を示す。

#### 周波数条件

|          |                             |

|----------|-----------------------------|

| ナイキスト帯域幅 | $f_{Nyq} = 1.728\text{GHz}$ |

| チャネル帯域幅  | $f_{CH} = 2.16\text{GHz}$   |

#### 受信感度条件

| CASE | 変調    | 最小受信感度 |

|------|-------|--------|

| 1    | BPSK  | -59dBm |

| 2    | 16QAM | -46dBm |

図 8.18 60GHz 帯 WPAN 受信機要求性能

(1) まず CASE 1 の性能を満足する ADC の仕様を検討する。検討にあたり、以下を仮定する。

- サンプリング周波数 :  $f_s = 2.592\text{GHz} \rightarrow OSR = \frac{f_s}{f_{Nyq}} = 1.5$

- ADC の量子化雑音による  $CNR_{total}$  特性の劣化率 :  $\gamma = -0.5\text{dB} \left( = \frac{1}{1.122} \right)$

- 受信機 NF :  $F = 10(NF = 10\text{dB})$

- 受信機入力端での雑音電力 :

$$P_{N0} = k_B T_a f_{Nyq} = 1.38 \times 10^{-23} \times 300 \times 1.728 \times 10^9 = 7.15 \times 10^{-12} \text{W} (-81.5\text{dBm})$$

$$(k_B : ボルツマン定数 (1.38 \times 10^{-23} \text{J/K}), T_a : 室温 (300\text{K}))$$

- 受信機入力端での信号電力  $P_{S0}$  (= 最小受信感度  $P_{S0,min}$ ) :

$$P_{S0} = 1.26 \times 10^{-9} W (-59 dBm)$$

- 受信機入力端での  $CNR$  :  $CNR_{in} = \frac{P_{S0}}{P_{N0}} = \frac{1.26 \times 10^{-9}}{7.15 \times 10^{-12}} = 176 (22.5 dB)$

- ピーカクファクタ ( $BPSK$  の場合) :  $par = 1.6 (2 dB)$

以上のパラメータを式 (8.51) に代入して以下が得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{2}{3} \times \frac{1.6 \times 176}{1.5 \times 10} \times \frac{1}{0.122} \right) = 3.3 \text{ (ビット)}$$

(2) 次に CASE 2 の性能を満足する ADC の仕様を検討する。上記 CASE 1 に比べて異なる部分は以下の 3 項目である。

- 受信機入力端での信号電力  $P_{S0}$  (=最小受信感度  $P_{S0,min}$ ) :

$$P_{S0} = 2.51 \times 10^{-8} W (-46 dBm)$$

- 受信機入力端での  $CNR$  :  $CNR_{in} = \frac{P_{S0}}{P_{N0}} = \frac{2.51 \times 10^{-8}}{7.15 \times 10^{-12}} = 3510 (33.5 dB)$

- ピーカクファクタ ( $16QAM$  の場合) :  $par = 2 \times 2.9 (7.6 dB)$

以上のパラメータを式 (8.54) に代入して以下が得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{1}{3} \times \frac{2 \times 2.9 \times 3510}{1.5 \times 10} \times \frac{1}{0.122} \right) = 5.9 \text{ (ビット)}$$

ここで得られたビット数  $b$  の値は、ADC のひずみ特性等による付加雑音も含んで実現する必要があり、ENOB と考えるべきものである。これから、設計する ADC のビット数  $b_{design}$  はマージンをもたせたものにする必要がある。

例えば、

$$\text{設計ビット数 } b_{design} = 7 \text{ (ビット)}$$

$$\text{動作周波数 } f_s = 2.592 GHz$$

とすれば、 $CNR_{total}$  特性の劣化率  $\gamma = -0.5dB$  の条件のもと、CASE 1 については 3.7 ビットのマージンを有して適用できる。CASE 2 についてはマージンが 1.1 ビットと小さいがこの場合にも適用できる。

#### 8.4.2 5GHz 帯マルチキャリア（OFDM）通信用 ADC

マルチキャリア（OFDM）通信の例として、IEEE802.11a 対応 5GHz 帯 WLAN (Wireless Local Area Network) システム<sup>[8]</sup>を取り上げ、その受信機に用いられる ADC の仕様について検討する。図 8.19 に受信機に対する要求性能（の一部）を示す。

周波数条件

$$\begin{aligned} f_{CH} &= 20MHz = Mf_0 + 2\Delta f_G \\ f_{CH} &; \text{チャネル帯域幅} \\ Mf_0 &; \text{周波数占有帯域幅} \\ \Delta f_G &; \text{周波数ガードバンド} \\ f_s &; \text{サンプリング周波数} \end{aligned}$$

受信感度条件

| CASE | 1次変調  | 最小受信感度 |

|------|-------|--------|

| 1    | 16QAM | -74dBm |

| 2    | 64QAM | -65dBm |

図 8.19 5GHz 帯 WLAN 受信機要求性能

(1) まず CASE 1 の性能を満足する ADC の仕様を検討する。検討にあたり、以下を仮定する。

- ・サンプリング周波数 :  $f_s = 30MHz \rightarrow OSR = \frac{f_s}{f_{CH}} = 1.5$

- ・ADC の量子化雑音による  $CNR_{out}$  特性の劣化率 :  $\gamma = -0.5dB \left( = \frac{1}{1.122} \right)$

- ・受信機 NF :  $F = 5.25 (NF = 7.2dB)$

- ・受信機入力端での雑音電力 :

$$P_{N0} = k_B T_a f_{CH} = 1.38 \times 10^{-23} \times 300 \times 20 \times 10^6 = 8.28 \times 10^{-14} W (-100.8dBm)$$

$$(k_B: \text{ボルツマン定数 } (1.38 \times 10^{-23} J/K), T_a: \text{室温 } (300K))$$

- 受信機入力端での信号電力  $P_{S0}$  (=最小受信感度  $P_{S0,\min}$ ) :

$$P_{S0} = 3.98 \times 10^{-11} W (-74 dBm)$$

- 受信機入力端での  $CNR$  :  $CNR_{in} = \frac{P_{S0}}{P_{N0}} = \frac{3.98 \times 10^{-11}}{8.28 \times 10^{-14}} = 480.7 (26.8 dB)$

- ピーカンファクタ ( $OFDM$  の場合) :  $par = 2 \times 3.5^2 (13.9 dB)$

以上のパラメータを式 (8.62) に代入して以下が得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{1}{3} \times \frac{2 \times 3.5^2 \times 480.7}{1.5 \times 5.25} \times \frac{1}{0.122} \right) = 6.0 \text{ (ビット)}$$

(2) 次に CASE 2 の性能を満足する ADC の仕様を検討する。上記 CASE 1 に比べて異なる部分は以下の 2 項目である。

- 受信機入力端での信号電力  $P_{S0}$  (=最小受信感度  $P_{S0,\min}$ ) :

$$P_{S0} = 3.16 \times 10^{-10} W (-65 dBm)$$

- 受信機入力端での  $CNR$  :  $CNR_{in} = \frac{P_{S0}}{P_{N0}} = \frac{3.16 \times 10^{-10}}{8.28 \times 10^{-14}} = 3816 (35.8 dB)$

以上のパラメータを式 (8.62) に代入して以下が得られる。

$$b = \frac{1}{2 \log 2} \log \left( \frac{1}{3} \times \frac{2 \times 3.5^2 \times 3816}{1.5 \times 5.25} \times \frac{1}{0.122} \right) = 7.5 \text{ (ビット)}$$

ここで得られたビット数  $b$  の値は、ADC のひずみ特性等による付加雑音も含んで実現する必要があり、ENOB と考えるべきものである。これから、設計する ADC のビット数  $b_{design}$  はマージンをもたせたものにする必要がある。

例えば、

$$\text{設計ビット数 } b_{design} = 8 \text{ (ビット)}$$

$$\text{動作周波数} \quad f_s = 30\text{MHz}$$

とすれば、 $CNR_{total}$  特性の劣化率  $\gamma = -0.5\text{dB}$  の条件のもと、CASE 1 については 2.0 ビットのマージンを有して適用できる。CASE 2 についてはマージンが 0.5 ビットと小さいがこの場合にも適用できる。

### 8.5 ADC の回路構成と動作

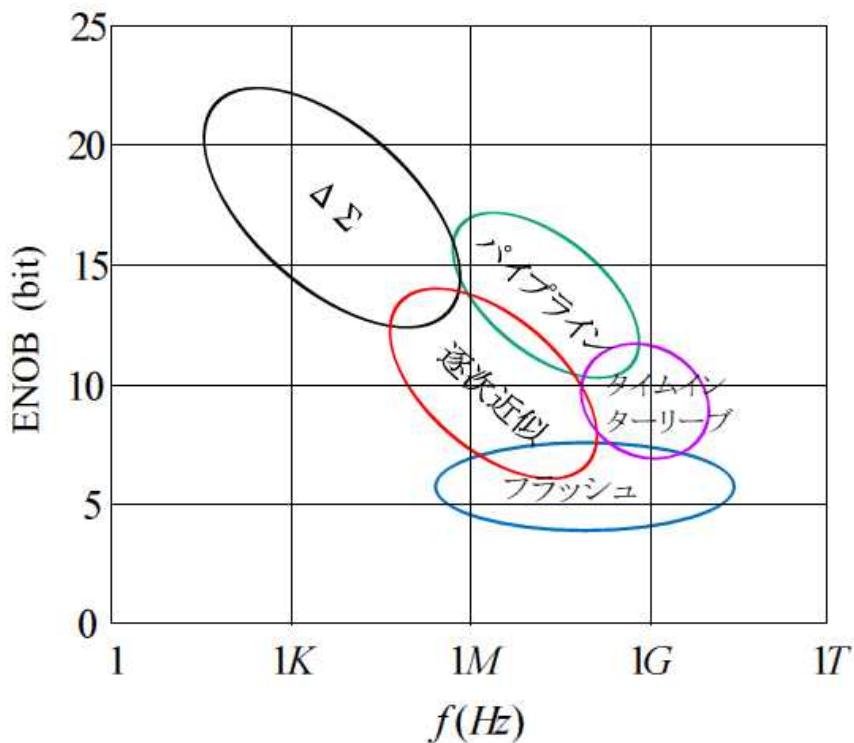

ADC の性能指標として、(a) 分解能 ( $ENOB$ )、(b) 動作周波数 ( $f$ )、(c) 消費電力があり、これらは ADC の回路方式に依存する。図 8.20 に ADC の回路方式と性能指標のうちの(a) 分解能 ( $ENOB$ ) と(b) 動作周波数 ( $f$ ) との関係を示す。

図 8.20 ADC の回路方式と分解能 ( $ENOB$ )、動作周波数 ( $f$ )

本節では ADC の回路方式として、(1) フラッシュ型、(2) 逐次近似 (SAR) 型、(3) パイプライン型、(4)  $\Delta\Sigma$  型、を取り上げ、その回路構成および動作について述べる。ただし、(4)  $\Delta\Sigma$  型については 8.8 節で述べる。

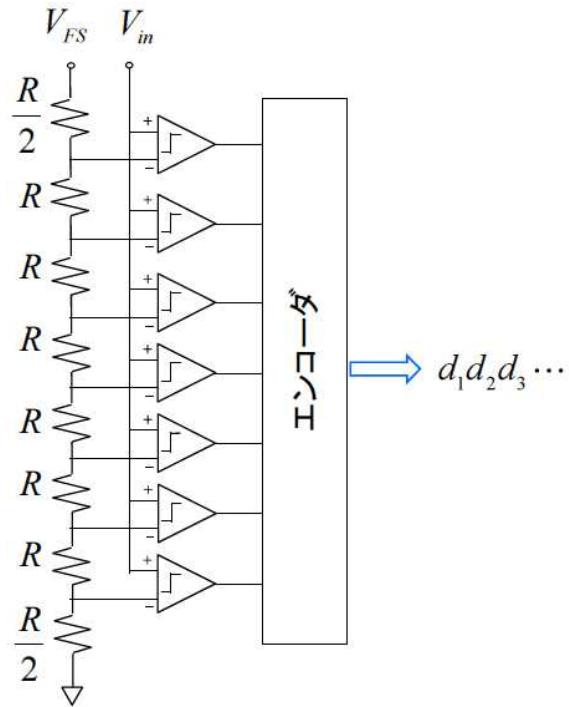

### 8.5.1 フラッシュ型 ADC

図 8.21 にフラッシュ型 ADC の回路構成を示す。

図 8.21 フラッシュ型 ADC の回路構成

フラッシュ型 ADC は、抵抗ラダーと複数の並列動作するコンパレータ群とエンコーダとから構成される。参照電圧  $V_{FS}$  ( $V_{FS}$  はフルスケール電圧でもある) と抵抗ラダーにより電圧ステップ（電圧の目盛り）を作り、各電圧ステップの値とサンプリングされた入力電圧  $V_{in}$ との大きさをコンパレータで比較し、 $V_{in}$  の値に対応する温度計コードを得る。得られた温度計コードはエンコーダ部でバイナリコード（バイナリ符号）に変換される。

入力電圧  $V_{in}$  と各電圧ステップの値との比較は並列配置されたコンパレータによりサンプリング時間ごとに一度に行われる。これにより高速なデータ変換が可能となる。しかし、 $N$ ビットのフラッシュ型 ADCを得る場合、電圧ステップ数は  $2^N - 1$  個となり、これを得るための抵抗の数は  $2^N$  個、コンパレータの数は  $2^N - 1$  個となり、 $N$  の増大と共にこれらの個数が指数関数で増大して行く。 $N$  が

大きくなるとチップ面積が増大し、また、抵抗、コンパレータのばらつきや特性変動などにより分解精度が低下する問題が出てくる。

これから、フラッシュ型 ADC は、ビット数  $N$  は比較的小さいが高速動作する領域で用いられる。

### 8.5.2 逐次近似 (SAR) 型 ADC

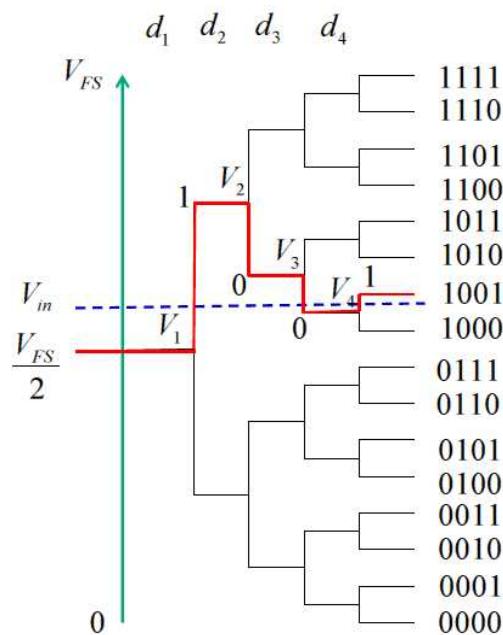

逐次近似型 ADC は SAR(Successive Approximation Register)型 ADC とも呼ばれる。参照電圧  $V_{FS}$  で与えたフルスケール電圧範囲の中で、サンプリングされた入力信号電圧  $V_{in}$  がどの位置にあるかを逐次的に求めるものである。すなわち電圧範囲を  $\frac{1}{2}$  づつ逐次的に分割していき、 $V_{in}$  がどこに存在するかを求め、その過程を通じてバイナリ符号化デジタル信号の値を得るものである。

図 8.22 は 4 ビットの場合を例に逐次近似型 ADC の動作原理を説明するものである。

図 8.22 逐次近似型 ADC の動作原理説明 (4 ビットの場合)

図の破線で示した  $V_{in}$  が入力されるものとする。 $V_{in}$  は、はじめの分岐部電圧

$V_1 = \frac{V_{FS}}{2}$  と大きさが比較される。この場合は  $V_{in} - V_1 = V_{in} - \frac{V_{FS}}{2} \geq 0$  となっており、

最初のビット  $d_1$  を 1 とし次の分岐に進む。 $V_{in}$  は次の分岐部電圧  $V_2 = \frac{V_{FS}}{2} \left(1 + \frac{1}{2}\right)$  と大きさが比較され、そこでは  $V_{in} - V_2 = V_{in} - \frac{V_{FS}}{2} \left(1 + \frac{1}{2}\right) < 0$  となっており、次のビット  $d_2$  を 0 とし、さらに次の分岐に進む。このような処理を逐次的に続け、図の

赤線の経路を経て、バイナリ符号化デジタル信号  $(d_1 d_2 d_3 d_4) = (1001)$  が得られる。

$k$  番目の分岐部電圧  $V_k$  とビット  $d_k$  の関係を与える一般式は以下となる。

$$\begin{aligned} k=1 \text{ の時} \quad V_k &= V_1 = \frac{V_{FS}}{2} \\ k \geq 2 \text{ の時} \quad V_k &= \frac{V_{FS}}{2} \left(1 + \sum_{j=1}^{k-1} B_j \frac{1}{2^j}\right) \quad B_j = \begin{cases} 1 & (d_j = 1 \text{ の場合}) \\ -1 & (d_j = 0 \text{ の場合}) \end{cases} \end{aligned} \quad (8.63)$$

$$\begin{aligned} V_{in} - V_k \geq 0 \text{ の場合} \quad &\rightarrow \quad d_k = 1 \\ V_{in} - V_k < 0 \text{ の場合} \quad &\rightarrow \quad d_k = 0 \end{aligned} \quad (8.64)$$

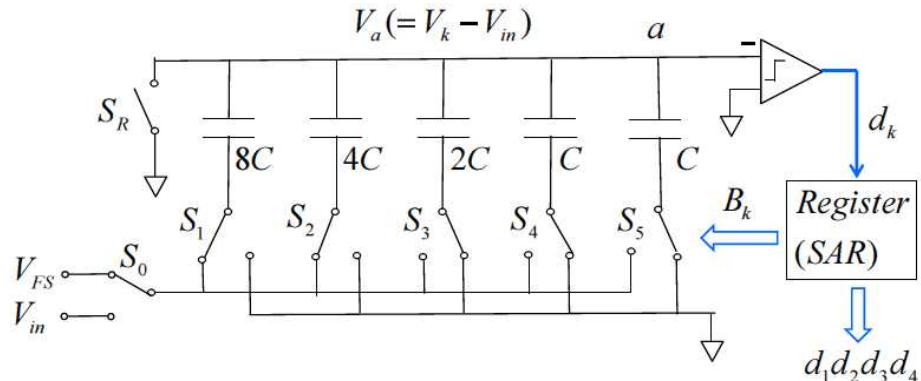

図 8.23 に逐次近似型 ADC の回路構成を示す。図は 4 ビットの場合を例に示している。この回路は容量による電荷再配分のメカニズムを用いることにより、上記の分岐部電圧  $V_k$  の生成と入力電圧  $V_{in}$  との減算を同時に行うことができる。

図 8.23 逐次近似型 ADC の回路構成 (4 ビットの場合)

以下、動作を説明する。

- ① 初めに、スイッチ  $S_R$  およびスイッチ  $S_1 \sim S_5$  をグランドに導通させ、容量の電荷を 0 とする。

- ②  $S_R$  をグランド側に導通したまま、スイッチ  $S_0$  および  $S_1 \sim S_5$  を入力信号電圧  $V_{in}$  側に導通させる。これにより、 $a$  点側に電荷  $Q_T = -16C \cdot V_{in}$  が生じる。

- ③  $S_R$  を開放し、 $S_1 \sim S_5$  をグランドに導通させる。これにより  $a$  点側に電荷  $Q_T = -16C \cdot V_{in}$  が保存される。この時、 $a$  点側の電圧は  $-V_{in}$  となっている。

- ④  $S_0$  を参照電圧  $V_{FS}$  側に導通させ、さらに  $S_1$  を  $V_{FS}$  側に導通させる ( $S_2 \sim S_5$  はグランドに導通のまま)。これにより、 $a$  点側の電圧は  $V_a = \frac{V_{FS}}{2} - V_{in}$  となる。コンパレータで  $V_a$  の正負を判定し、最初の（最上位の）ビット  $d_1$  の値が決まる。すなわち、 $V_a \leq 0$  ( $V_{in} - \frac{V_{FS}}{2} \geq 0$ ) の時  $d_1 = 1$  となり、 $V_a > 0$  ( $V_{in} - \frac{V_{FS}}{2} < 0$ ) の時  $d_1 = 0$  となる。

- ⑤  $d_1$  の値に応じて、式 (8.63) に従い、 $B_1$  さらに次の分岐部電圧  $V_2$  が求まる。

$V_2$  の値は以下で説明するように  $S_1 \sim S_5$  の接続の組み合わせで実現される。

- ⑥  $S_1 \sim S_5$  の接続の組み合わせを変えながら、上記④、⑤の手順を繰り返すことにより  $d_2$ ,  $d_3$ ,  $d_4$  が順次決められる。

ここで、 $V_k$  の値が  $S_1 \sim S_5$  の接続の組み合わせで実現されることを説明する。

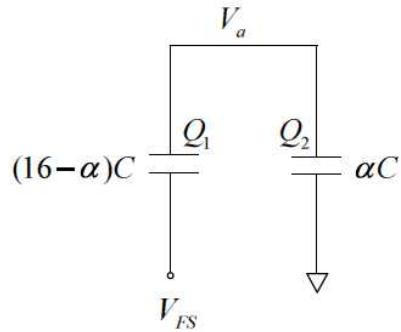

例えば、図 8.24 に示す様に、 $a$  点側の電荷  $Q_T = -16C \cdot V_{in}$  が保存された状態で、全容量  $16C$  のうち  $\alpha C$  をグランドに、 $(16-\alpha)C$  を  $V_{FS}$  に接続する場合を考える。

図 8.24 容量による電圧分割

この時、電荷保存則から以下の連立式が成り立つ。

$$\begin{aligned} Q_1 &= (16 - \alpha)C(V_a - V_{FS}) \\ Q_2 &= \alpha CV_a \\ Q_T = -16CV_{in} &= Q_1 + Q_2 \end{aligned} \quad \left. \right\} \quad (8.65)$$

これを解いて、以下が得られる。

$$\begin{aligned} V_a &= V_k - V_{in} \\ V_k &= \left(1 - \frac{\alpha}{16}\right)V_{FS} \end{aligned} \quad (8.66)$$

図 8.23 に示す容量構成の場合、スイッチ  $S_1 \sim S_5$  の接続の仕方により  $\alpha$  の値を 1

～15 の範囲で変化させることができる ( $V_k$  は  $\frac{15}{16}V_{FS} \sim \frac{1}{16}V_{FS}$  で変化する)。また、

式 (8.66) から、 $V_a$  は  $V_k$  から  $V_{in}$  を減算したものとして与えられることになる。

$N$  ビット逐次近似型 ADC では、サンプリングされた一つの入力信号  $V_{in}$  に対して、

$N$  回の逐次近似処理が必要であり、この処理を次の信号が入る時間までに完了させる必要がある。このため、ビット数の増大や高速化に制約が出てくる。しかし、この方式では、使用コンパレータが 1 個で構成がシンプルであり、また、容量を用いる構成のため静止電流が流れず低消費電力動作が可能であるという優れた特長を有している。近年の素子微細化による高速化の性能改善とあいま

って広い領域で使われるようになってきている。

### 8.5.3 パイプライン型 ADC

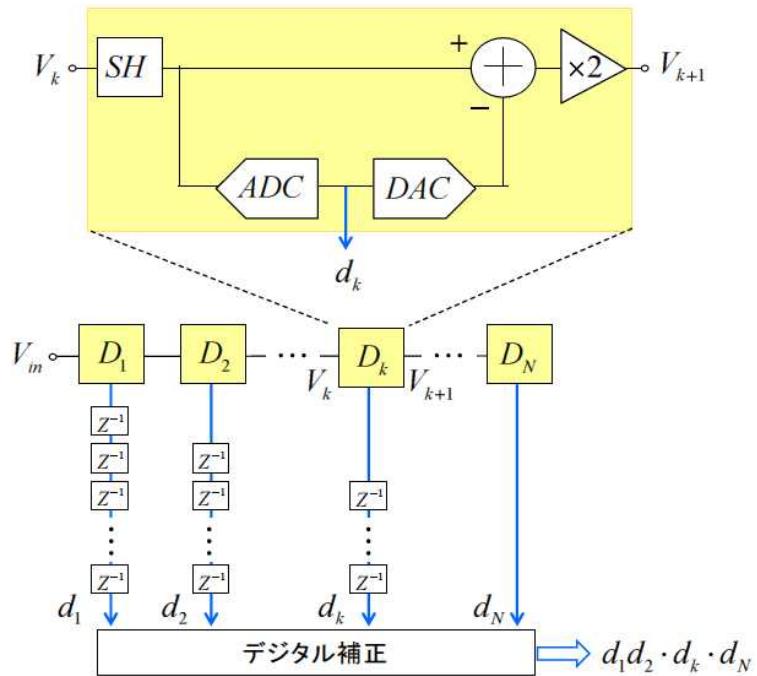

図 8.25 に  $N$  ビットパイプライン型 ADC の構成ブロックを示す。同一構成のサブ回路  $D_k$  ( $k = 1, 2, \dots, N$ ) が  $N$  段カスケード接続され、パイプライン動作する構成となっている。

図 8.25  $N$  ビットパイプライン型 ADC の構成ブロック

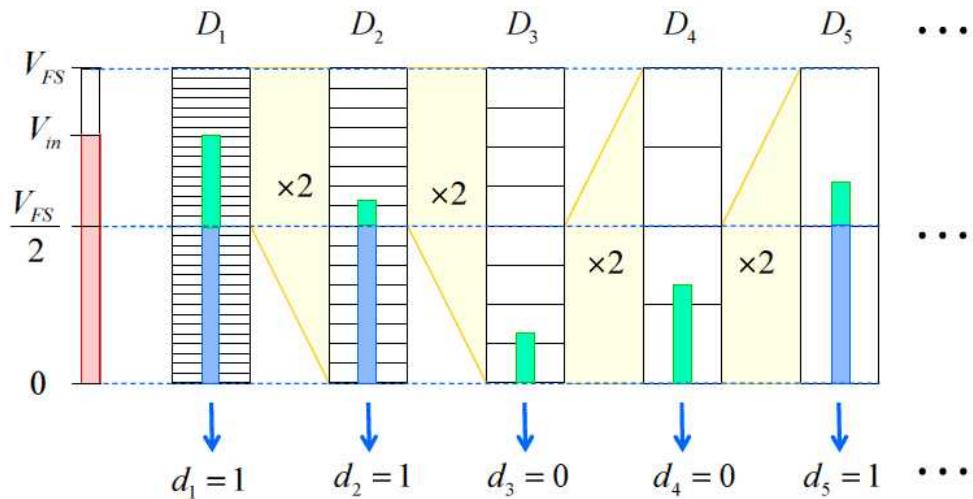

図 8.26 にパイプライン型 ADC による AD 変換動作の様子を示す。サンプリングされた入力信号  $V_{in}$  は、まず 1 段目のサブ回路  $D_1$  中の ADC で AD 変換され 1 ビットバイナリ信号  $d_1$  が出力される。そこででの量子化誤差は 2 倍に増幅され、2 段目サブ回路  $D_2$  の入力信号になる。 $D_2$  では、1 段目からの信号が AD 変換され次の 1 ビットバイナリ信号  $d_2$  が出力される。ここででの量子化誤差も 2 倍に増幅

され、3段目サブ回路  $D_3$  の入力信号になる。上記プロセスを順次繰り返すことにより、 $N$ ビットのバイナリ符号化デジタル信号  $d_1d_2\cdots d_k\cdots d_N$  が得られる。ここで、各サブ回路の量子化誤差を2倍に増幅するのは、各段に同一構成のサブ回路を用いることができるようにするためである。

図 8.26 パイプライン型 ADC による AD 変換動作の様子

ある時刻にサンプリングされた入力信号  $V_{in}$  に対して各サブ回路では異なる時刻にAD変換が行われる。このため、各サブ回路からのバイナリ信号  $d_k (k = 1, 2, \dots, N)$  を出力するタイミングをそろえるために、図 8.25 に示すように遅延素子  $z^{-1}$  が設けられている。

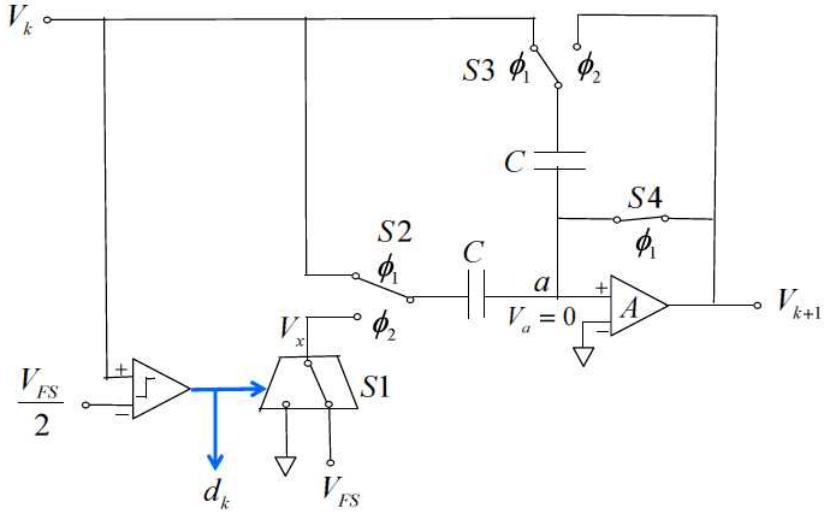

図 8.27 にサブ回路部分の回路構成とその動作を示す。入力されたアナログ信号電圧  $V_k$  はコンパレータで参照電圧  $\frac{V_{FS}}{2}$  ( $V_{FS}$  はフルスケール電圧) と比較され、

1ビットバイナリ信号  $d_k$  が出力される（1ビット AD 変換）。

$d_k$  の値に応じてスイッチ  $S1$  が切り替え制御され、以下で与えられるアナログ出力電圧  $V_x$  を得る（1ビット DA 変換）。

$$V_x = \begin{cases} 0 & (d_k = 0 \text{ の場合}) \\ V_{FS} & (d_k = 1 \text{ の場合}) \end{cases} \quad (8.67)$$

図 8.27 サブ回路の構成と動作

サブ回路中のスイッチ  $S2$ ,  $S3$ ,  $S4$ はサンプルモード時には  $\phi_1$  (側を導通した) 状態とする。この時,  $a$  点には電荷  $Q_T = -2CV_k$  が蓄積される。次に  $S2$ ,  $S3$  を  $\phi_2$  (側を導通した) 状態とし, また  $S4$  を開放とする。 $a$  点はオペアンプの仮想接地点であり,  $V_a = 0$  となっている。この時, 電荷保存則から以下の連立式が成り立つ。

$$\left. \begin{aligned} Q_1 &= -CV_X \\ Q_2 &= -CV_{k+1} \\ Q_T &= -2CV_k = Q_1 + Q_2 \end{aligned} \right\} \quad (8.68)$$

これを解いて, 以下が得られる。

$$V_{k+1} = 2V_k - V_X \quad (8.69)$$

式 (8.67), (8.69) から以下が得られる。

$$\left. \begin{array}{lll} 0 \leq V_k \leq \frac{V_{FS}}{2} の時 & d_k = 0 & V_{k+1} = 2V_k \\ \frac{V_{FS}}{2} \leq V_k \leq V_{FS} の時 & d_k = 1 & V_{k+1} = 2V_k - V_{FS} \end{array} \right\} \quad (8.70)$$

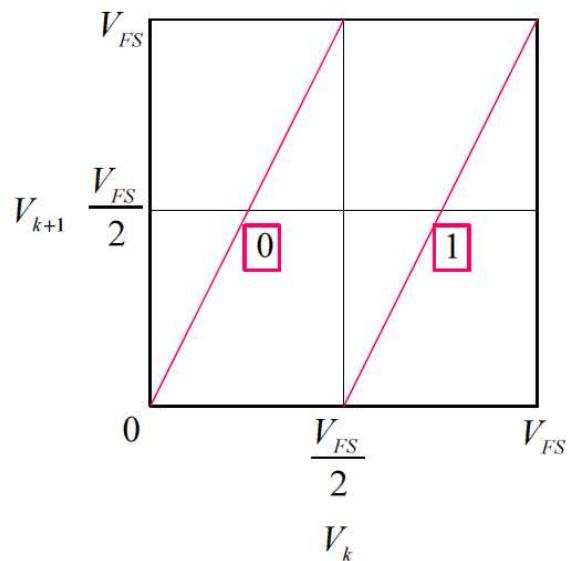

式 (8.70) から、スイッチの切り替え制御により、1 ビット AD 変換と、量子化誤差を 2 倍に増幅して次段に出力することが実現されている。図 8.28 に式 (8.70) で得られた結果を図示する。

図 8.28 サブ回路の動作

～1 ビット AD 変換と、量子化誤差を 2 倍に増幅して出力する～

図 8.29 にロバートソンプロットにより多段化したサブ回路から連続してバイナリ符号化デジタル信号（多ビットデジタル信号）を求める方法を示す。この方法は、奇数番目のサブ回路による AD 変換に対しては図の赤線の特性を、偶数番目のサブ回路による AD 変換に対しては図の青線の特性を、交互に用いることにより連続したバイナリ符号化デジタル信号の値を求めていくものである。図では例として、 $d_1d_2d_3d_4d_5 \cdots = 11001\cdots$  の場合について示している。

$$d_1 d_2 d_3 d_4 d_5 \dots = 11001\dots$$

図8.29 ロバートソンプロットにより多ビットデジタル信号を求める方法

これまで、サブ回路の中で1ビットのAD変換を行うとしたが、この部分は多ビットのAD変換にすることもできる。実際、コンパレータ部のオフセット誤差による変換誤りを低減するため、1.5ビットAD変換が一般に用いられる。

パイプライン動作では、時刻  $t_1$  でサンプリングされた信号  $V_{in}^{(t1)}$  を2段目サブ回路  $D_2$  で処理している時、1段目サブ回路  $D_1$  では次の時刻  $t_2$  でサンプリングされた信号  $V_{in}^{(t2)}$  の処理を行っている。以下同様であり、パイプライン型ADCではビット数  $N$  が大きくなっても、各サブ回路は1個のサンプリング入力信号に対してサンプリング時間間隔  $T_s$  内でAD変換処理を行えば良く、高速動作に適している。このことから、パイプライン型ADCはビット数が比較的大きく、かつ、高速動作する領域で用いられる。ただし、ビット数  $N$  を増大していくと、電圧ステップ幅  $\Delta$  と信号検出誤差とが同レベルとなるため、それが  $N$  の上限となる。パイプライン型ADCでは、電力消費が大きいオペアンプが各サブ回路に用いられる。このため、消費電力が比較的大きくなることが課題である。また、ビット数  $N$  増大に伴う入力信号に対する出力信号の遅延（レイテンシ）も制約要因となる。

## 8.6 DAC の回路構成と動作

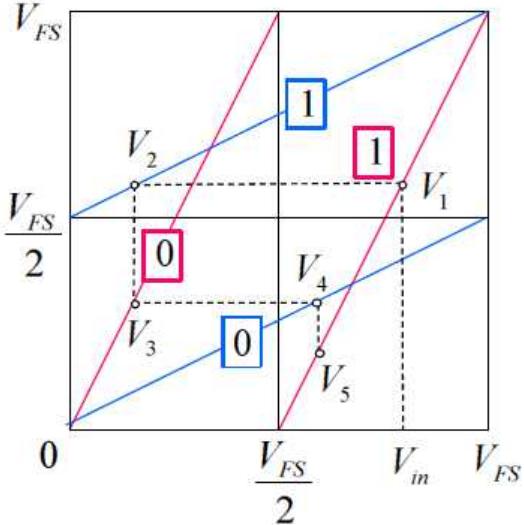

図 8.30 にデジタルからアナログへの変換ステップの概要を示す。図には、各ステップで得られる信号の時間波形と周波数スペクトルの様子を示している。

図 8.30 デジタルからアナログへの変換ステップの概要

デジタルからアナログへの変換は以下の 3 ステップで行われる。

- ① バイナリ符号化されたデジタル信号を復号化により離散インパルス信号に変換する。DAC の主要な機能は復号化の処理を行うことといえる。

- ② 離散インパルス信号を再生フィルタリングによりステップパルス信号に変換する。再生フィルタリングを行う具体的な回路は DAC 内のサンプル・ホールド回路やラッチ回路等であり、実際の DAC では①と②のステップが同時に行われるのが一般的である。

- ③ ステップパルス信号を低域フィルタリングして連続アナログ信号を得る。

本節では DAC の回路方式として、(1) 抵抗ラダーによる電圧分圧デコード型、

(2) R-2R 抵抗による電流加算バイナリ型, (3) 容量による電荷転送バイナリ型, を取り上げ, その回路構成および動作を述べる。

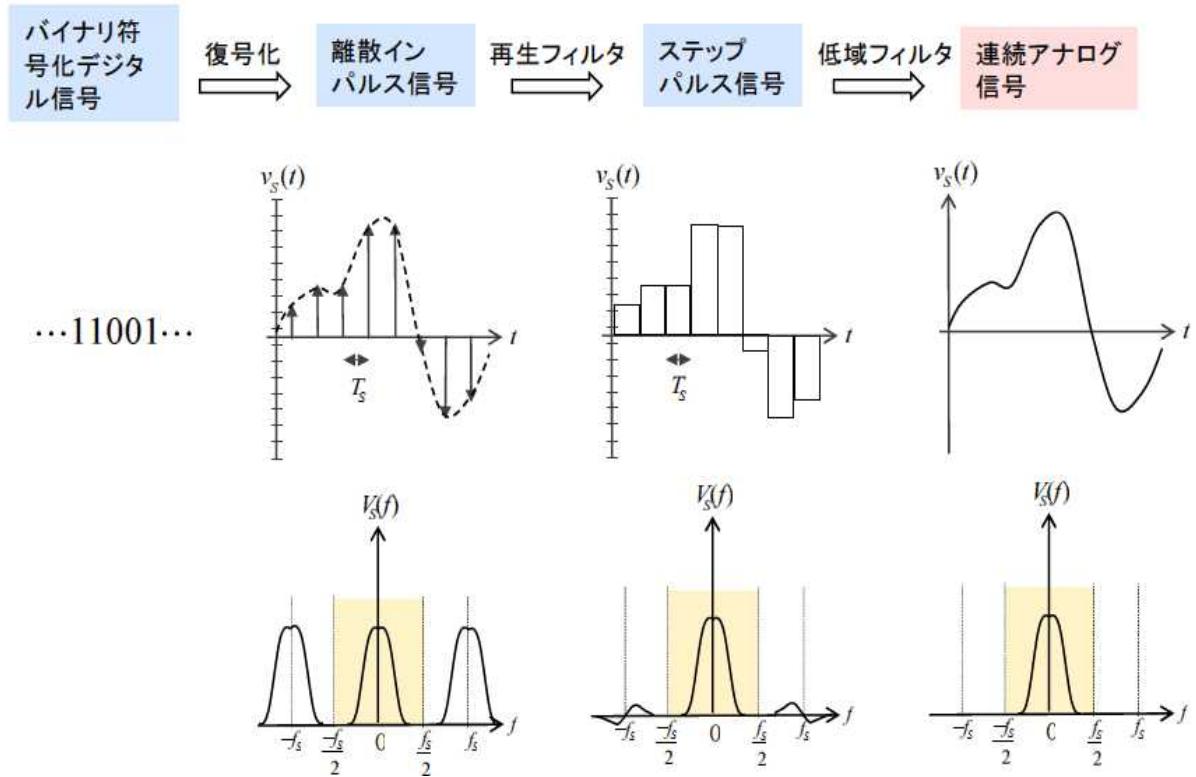

### 8.6.1 抵抗ラダーによる電圧分圧デコード型 DAC

図 8.31 に抵抗ラダーによる電圧分圧デコード型 DAC の回路構成を示す。

図 8.31 抵抗ラダーによる電圧分圧デコード型 DAC の回路構成

$N$  ビット DAC の場合,  $2^N$  個の抵抗およびスイッチ (ここでは MOSFET を使用), および, デコーダとユニティゲインバッファで構成される。参照電圧  $V_{FS}$  ( $V_{FS}$  はフルスケール電圧でもある) を抵抗ラダーにより電圧間隔  $\Delta = \frac{V_{FS}}{2^N}$  で分圧し,  $0 \sim V_{FS}$  の電圧範囲に  $2^N$  個の電圧ステップを生成する。入力 (バイナリ符号化) デジタル信号  $d_1d_2d_3\cdots$  はデコードされ, 対応する電圧ステップのスイッチ (MOSFET) のみをオン (導通) させ, 次式で与えられるアナログ電圧  $V_{out}$  を取り出す。

$$V_{out} = \frac{V_{FS}}{2^N} \sum_{k=1}^N d_k \frac{1}{2^k} \quad (d_k = 0,1) \quad (8.71)$$

得られた  $V_{out}$  はユニティゲインバッファにより、負荷回路の影響を受けることなく出力される。

この DAC のビット数  $N$  の上限は素子の統計的ばらつきなどにより誤差が電圧間隔  $\Delta = \frac{V_{FS}}{2^N}$  のオーダーになるところで制限される。

デコード型 DAC に一般に言えることであるが、この DAC の長所として、設定電圧値の増大（減少）に伴って出力電圧値も単調に増大（減少）する単調動作をすることがある。

### 8.6.2 R-2R 抵抗による電流加算バイナリ型 DAC

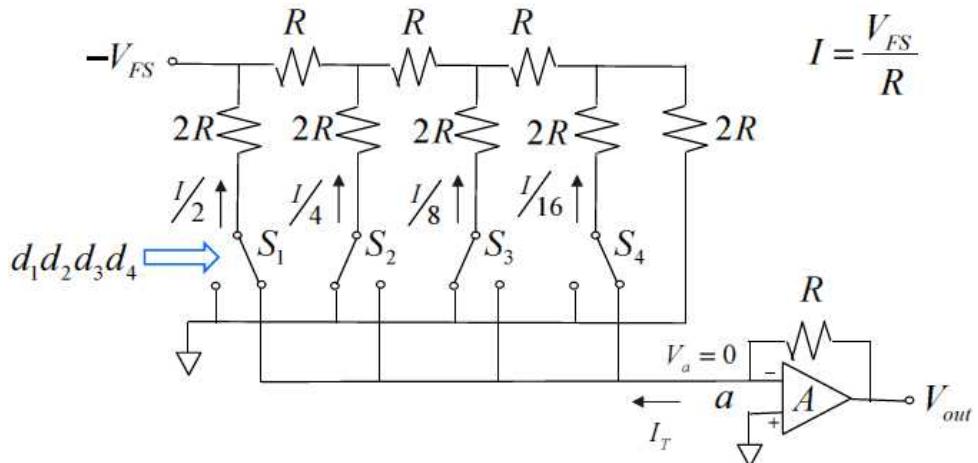

図 8.32 に R-2R 抵抗による電流加算バイナリ型 DAC の回路構成を示す。図は例として 4 ビットの場合を示している。

図 8.32 R-2R 抵抗による電流加算バイナリ型 DAC の回路構成

この DAC は 2 種類の抵抗  $R$  と  $2R$  を用いて構成される。ここで参考電圧  $-V_{FS}$  ( $V_{FS}$  はフルスケール電圧) を印加すると、スイッチと接続されている各  $2R$  抵抗部分には図のように  $\frac{I}{2} \left( = \frac{I}{2^0} \right)$ ,  $\frac{I}{4} \left( = \frac{I}{2^2} \right)$ ,  $\frac{I}{8} \left( = \frac{I}{2^3} \right)$ ,  $\frac{I}{16} \left( = \frac{I}{2^4} \right)$  ( $I = \frac{V_{FS}}{R}$ ) の電流が

流れる。入力（バイナリ符号化）デジタル信号  $d_1d_2d_3d_4$  に応じてスイッチ  $S_1 \sim S_4$  が切り替えられ、電流はグランド側に流れるものと  $a$  点側に流れるものに分けられる。具体的には  $k$  番目デジタルビットが  $d_k = 0$  の時スイッチ  $S_k$  はグランド側に導通、 $d_k = 1$  の時  $S_k$  は  $a$  点側に導通される。この結果  $a$  点側を流れる全電流  $I_T$  は次式で与えられる。

$$I_T = \frac{V_{FS}}{R} \sum_{k=1}^4 d_k \frac{1}{2^k} \quad (d_k = 0,1) \quad (8.72)$$

$a$  点はオペアンプの仮想接地点であり、 $V_a = 0$  となっている。これから、電流  $I_T$  と出力電圧  $V_{out}$  には次式の関係式がなりたつ。

$$V_{out} = I_T R \quad (8.73)$$

式 (8.72) と (8.73) から次式が得られる。

$$V_{out} = V_{FS} \sum_{k=1}^4 d_k \frac{1}{2^k} \quad (d_k = 0,1) \quad (8.74)$$

式 (8.74) は入力された（バイナリ符号化）デジタル信号  $d_1d_2d_3d_4$  がアナログ出力電圧  $V_{out}$  に DA 変換されたことを示している。

$N$  ビットの R-2R 抵抗による電流加算バイナリ型 DAC の場合、用いる 2R の抵抗の数は  $N+1$  個、R の抵抗の数は  $N$  個である。これから、 $N$  が大きくなってしまって回路規模が極端には大きくならない利点がある。また、抵抗値は  $R$  と  $2R$  の 2 種類のみなので、抵抗素子製作上の問題（誤差）が小さい利点もある。

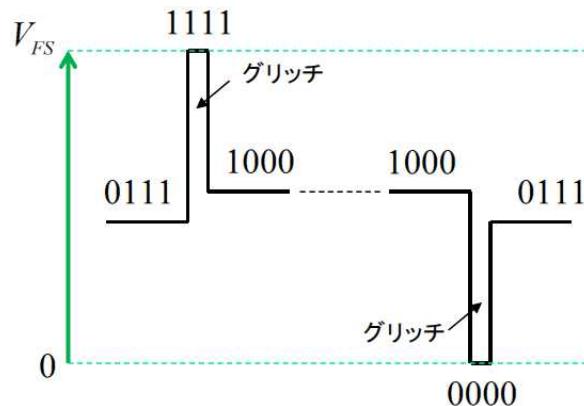

ただし、バイナリ型 DAC に一般に言えることであるが、スイッチ切り替えタイミングのわずかなずれによりグリッヂが生じる問題がある。図 8.33 に 4 ビットの場合についてグリッヂ発生の様子を示す。グリッヂは信号に依存して生じる

のでランダムなひずみのような振る舞いをする。グリッヂのエネルギーが大きい上位ビット部分にデコード型 DAC を用い、グリッヂエネルギーが小さい下位ビット部分にバイナリ型 DAC を用いるセグメント構成により、グリッヂの影響を低減することも行われている。

図 8.33 グリッヂ発生の様子（4 ビットの場合）

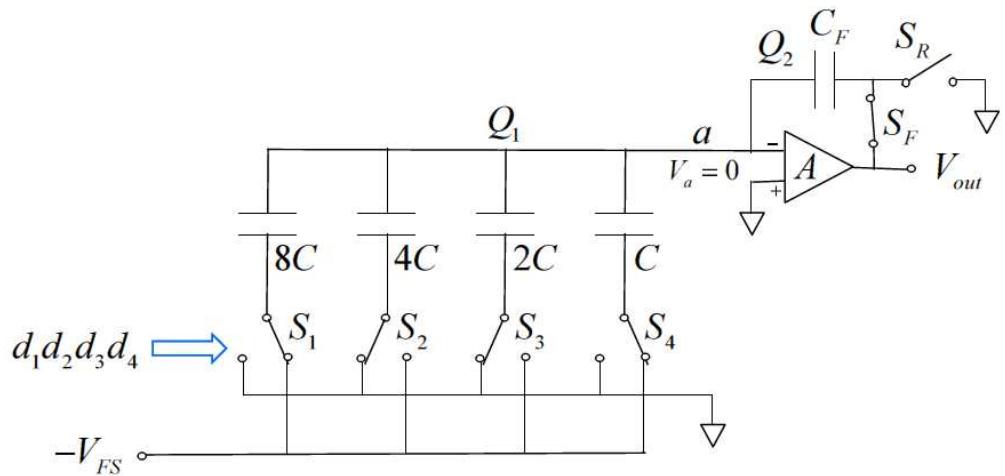

### 8.6.3 容量による電荷転送バイナリ型 DAC

図 8.34 に容量による電荷転送バイナリ型 DAC の回路構成を示す。図は例として 4 ビットの場合を示している。

4 ビットの場合、 $C (= 2^0 C) \sim 8C (= 2^3 C)$  および  $C_F (= C)$  の容量、スイッチ  $S_1 \sim S_4$ 、

$S_F$ 、 $S_R$  およびオペアンプで構成される。

以下、動作を説明する。

① 初めに、スイッチ  $S_F$  を開放、スイッチ  $S_R$  およびスイッチ  $S_1 \sim S_4$  をグランドに導通させる。これにより、すべての容量の電荷を 0 とする。

②  $S_R$  を開放、 $S_F$  を導通させ、さらに、入力（バイナリ符号化）デジタル信号

$d_1 d_2 d_3 d_4$  に応じてスイッチ  $S_1 \sim S_4$  を切り替える。この時、以下で述べるように容

量  $C_F (= C)$  を介して出力電圧  $V_{out}$  が得られる。

図 8.34 容量による電荷転送バイナリ型 DAC の回路構成

以下  $V_{out}$  が得られるメカニズムを述べる。

上記②のプロセスにおいて、容量  $C (= 2^0 C) \sim 8C (= 2^3 C)$  の  $a$  点側に発生する電荷  $Q_1$  は次式で与えられる。ここで、 $a$  点はオペアンプの仮想接地点で、 $V_a = 0$  であることを用いている。

$$Q_1 = V_{FS} C \sum_{k=1}^4 d_k 2^{4-k} \quad (d_k = 0, 1) \quad (8.75)$$

また、容量  $C_F$  の  $a$  点側に発生する電荷  $Q_2$  は次式で与えられる。

$$Q_2 = -V_{out} C_F \quad (8.76)$$

$a$  点側の全電荷  $Q_T$  は 0 であるので、電荷保存則から次式が成り立つ。

$$Q_T = 0 = Q_1 + Q_2 \quad (8.77)$$

式 (8.75) ~ (8.77) から次式が得られる。

$$V_{out} = V_{FS} \frac{C}{C_F} \sum_{k=1}^4 d_k 2^{4-k} = V_{FS} \sum_{k=1}^4 d_k 2^{4-k} \quad (d_k = 0, 1) \quad (8.78)$$

式 (8.78) は入力された (バイナリ符号化) デジタル信号  $d_1 d_2 d_3 d_4$  がアナログ出力電圧  $V_{out}$  に DA 変換されたことを示している。

この DAC は容量を用いる構成のため静止電流が流れないので、抵抗を用いる構成に比較して低消費電力動作である特長を有している。ただし、デコード型に特有なグリッチ発生の問題は残るので適切な対策は必要である。

## 8.7 $\Delta \Sigma$ 変調 ADC/DAC のための Z 変換技術

### 8.7.1 Z 変換とは

$\Delta \Sigma$  変調などのデジタル信号処理技術を学ぶ上で、Z 変換を理解しておくことが必要となる。ここでは Z 変換の基礎的なことについて述べる。

離散時間信号系列  $\{f(n)\}$  の Z 変換  $F(z)$  は次式で定義される。

$$F(z) = Z(f(n)) = \sum_{n=0}^{\infty} f(n)z^{-n} \quad (8.79)$$

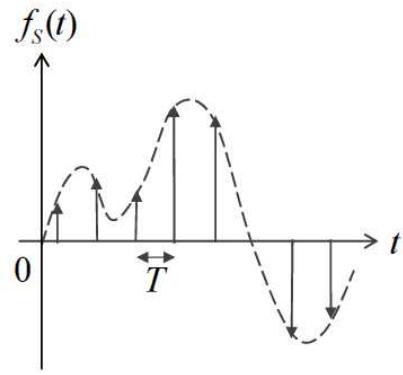

Z 変換は、以下に示すように離散時間信号  $f_s(t)$  をラプラス変換したものと考えることができる。なお、ラプラス変換および Z 変換については参考図書[6]等を参照のこと。

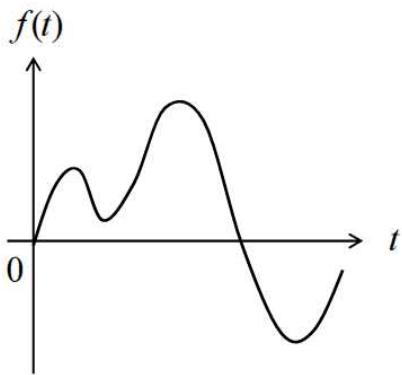

図 8.35 に (a) 連続時間信号  $f(t)$  とそれを時間間隔  $T$  でサンプリングした (b) 離散時間信号  $f_s(t)$  を示す。ここで、 $f(t)$ 、 $f_s(t)$  は  $t \geq 0$  で定義され、 $t < 0$  では

$f(t) = 0$ 、 $f_s(t) = 0$  であるとする。

(a) 連続時間信号  $f(t)$

(b) 離散時間信号  $f_s(t)$

図 8.35 連続時間信号と離散時間信号

$f_s(t)$  はデルタ関数  $\delta(t)$  を用いて次式で表わすことができる。

$$f_s(t) = \sum_{n=0}^{\infty} f(nT) \delta(t - nT) \quad (8.80)$$

ここで、

$$\delta(t) = \begin{cases} \infty & (t = 0) \\ 0 & (t \neq 0) \end{cases} \quad (8.81)$$

$$\int_{-\infty}^{\infty} \delta(t) dt = 1$$

式 (8.80) をラプラス変換することにより次式が得られる。

$$\begin{aligned} L(f_s(t)) &= F_s(s) = \int_0^{\infty} f_s(t) e^{-st} dt = \int_0^{\infty} \sum_{n=0}^{\infty} f(nT) \delta(t - nT) e^{-st} dt \\ &= \sum_{n=0}^{\infty} f(nT) \int_0^{\infty} \delta(t - nT) e^{-st} dt = \sum_{n=0}^{\infty} f(nT) e^{-snT} \end{aligned} \quad (8.82)$$

式 (8.82)において、 $e^{sT} \rightarrow z$  ,  $f(nT) \rightarrow f(n)$  ,  $F_s(s) \rightarrow F(z)$  , と置き換えることにより Z 変換の定義を与える式 (8.79) が得られる。

### 8.7.2 基本的な離散時間信号のZ変換

(a) 指数関数信号

$$x(n) = a^n \quad (n \geq 0) \quad (8.83)$$

$$Z(x(n)) = \sum_{n=0}^{\infty} x(n)z^{-n} = \sum_{n=0}^{\infty} a^n z^{-n} = \frac{1}{1 - az^{-1}} = \frac{z}{z - a} \quad (8.84)$$

ここで、以下の信号の収束条件を満足する必要がある

$$|az^{-1}| < 1 \rightarrow |z| > |a| \quad (8.85)$$

(b) 単位ステップ信号

$$u(n) = 1 \quad (n \geq 0) \quad (8.86)$$

式 (8.83), (8.84)において、 $a=1$ とすればよい。

$$Z(u(n)) = \sum_{n=0}^{\infty} u(n)z^{-n} = \sum_{n=0}^{\infty} z^{-n} = \frac{1}{1 - z^{-1}} = \frac{z}{z - 1} \quad (8.87)$$

(c) 単位インパルス信号

$$\delta(n) = \begin{cases} 1 & (n = 0) \\ 0 & (n \neq 0) \end{cases} \quad (8.88)$$

$$Z(\delta(n)) = \sum_{n=0}^{\infty} \delta(n)z^{-n} = 1 \quad (8.89)$$

任意の離散時間信号  $x(n)$  は単位インパルス信号  $\delta(n)$  を用いた次式で表わすことができる。

$$x(n) = \sum_{k=0}^{\infty} x(k)\delta(n-k) \quad (8.90)$$

連続時間信号系において式 (8.81) で与えられたデルタ関数  $\delta(t)$  は,  $t=0$ において  $\delta(t)=\infty$  となるのに対して, 離散時間信号系における単位インパルス信号  $\delta(n)$  は,  $n=0$  において  $\delta(n)=1$  となることに注意する必要がある。

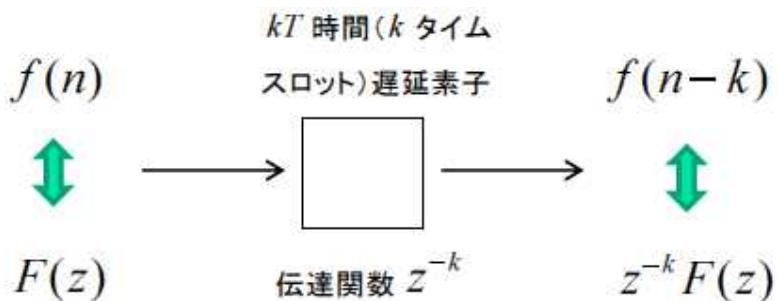

#### (d) 時間シフト

$Z(f(n))=F(z)$  の時,  $f(n)$  を  $kT$  時間シフトした  $f(n-k)$  の  $Z$  変換は以下となる。

$$\begin{aligned} Z(f(n-k)) &= \sum_{n=0}^{\infty} f(n-k)z^{-n} = \sum_{n'=-k}^{\infty} f(n')z^{-n'}z^{-k} \\ &= z^{-k} \sum_{n'=0}^{\infty} f(n')z^{-n'} = z^{-k}F(z) \end{aligned} \quad (8.91)$$

式 (8.91) で与えられる時間シフトのブロック図を図 8.36 に示す。  $Z$  領域では  $k$  タイムスロットの時間遅延を  $Z^{-k}$  の伝達関数で表わすことができる。

図 8.36 時間シフトのブロック図

### 8.7.3 線形時不变離散時間システムの入出力応答

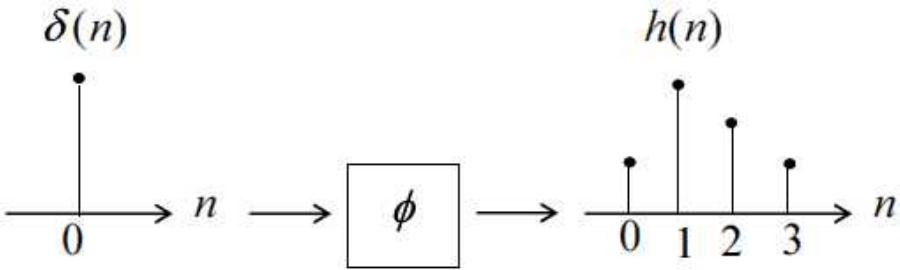

次式のインパルス応答  $h(n)$  を有する線形時不变システム  $\phi$  を考える。

$$h(n) = \phi(\delta(n)) \quad (8.92)$$

図 8.37 にインパルス応答例を模式的に示す。

図 8.37 インパルス応答例

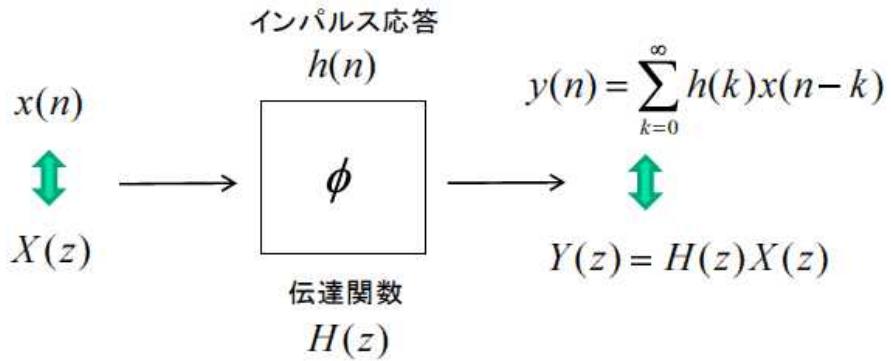

システム  $\phi$  に任意の離散時間信号  $x(n)$  が入力されたときの出力離散時間信号  $y(n)$  を求める。  $x(n)$  として式 (8.90) を用いると  $y(n)$  は次式で表わせる。

$$y(n) = \phi(x(n)) = \phi\left(\sum_{k=0}^{\infty} x(k)\delta(n-k)\right) \quad (8.93)$$

システムが線形時不变であることから、  $y(n)$  はさらに次式で表わせる。

$$y(n) = \sum_{k=0}^{\infty} x(k)\phi(\delta(n-k)) = \sum_{k=0}^{\infty} x(k)h(n-k) = \sum_{k=0}^{\infty} h(k)x(n-k) \quad (8.94)$$

式の最後の関係式はシステムが因果的 ( $h(n)=0$  ( $n<0$ )) であることから導かれる。式 (8.94) から、線形時不变離散時間システムにおける出力信号  $y(n)$  は入力信号  $x(n)$  とインパルス応答  $h(n)$  の離散たたみ込みで与えられると言える。式 (8.94) の  $Z$  変換は次式となる。

$$\begin{aligned} Y(z) &= Z(y(n)) = Z\left(\sum_{k=0}^{\infty} h(k)x(n-k)\right) = \sum_{n=0}^{\infty} \sum_{k=0}^{\infty} h(k)x(n-k)z^{-n} \\ &= \sum_{k=0}^{\infty} h(k)z^{-k} \sum_{n=0}^{\infty} x(n-k)z^{-n+k} = \sum_{k=0}^{\infty} h(k)z^{-k} \sum_{l=-k}^{\infty} x(l)z^{-l} \\ &= \sum_{k=0}^{\infty} h(k)z^{-k} \sum_{l=0}^{\infty} x(l)z^{-l} = H(z)X(z) \end{aligned} \quad (8.95)$$

$x(n)$  と  $h(n)$  の離散たたみ込みの  $Z$  変換はそれぞれの  $Z$  変換  $X(z)$  と  $H(z)$  の積で与えられる。 $H(z)$  はシステムの伝達関数と呼ばれる。

図 8.38 に線形時不变離散時間システムの入出力応答のブロック図を示す。

図 8.38 線形時不变離散時間システムの入出力応答のブロック図

#### 8.7.4 システムの安定性と周波数特性

連続時間システムにおける安定性はラプラス変換により得られた伝達関数  $H(s)$  (インパルス応答  $h(t)$ ) の極の位置により判定される。すなわち,  $H(s)$  のすべての極が  $\operatorname{Re}(s) \leq 0$  に存在する場合にシステムは安定であり, 逆に  $\operatorname{Re}(s) > 0$  に 1 つでも極が存在する場合には不安定となる (時間経過と共に出力信号が無限大に発散する)。

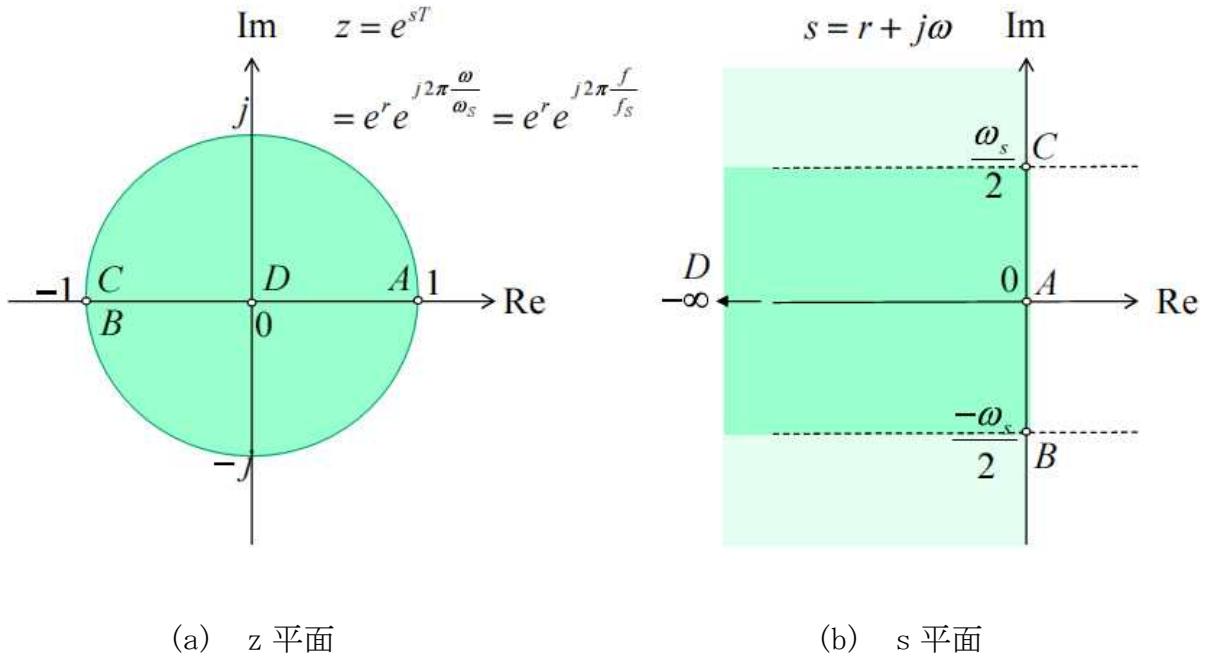

離散時間システムにおける  $Z$  変換の  $z$  は, 定義よりラプラス変換における  $s$  と次式で関係付けられる。

$$z = e^{sT} \quad (8.96)$$

式 (8.96) に従い,  $s$  を表わす複素平面 ( $s$  平面) は  $z$  を表わす複素平面 ( $z$  平面) に写像される。図 8.39 に  $s$  平面と  $z$  平面の関係を示す。 $s$  平面の A~D は  $z$  平面の A~D に対応する。すなわち,  $s$  平面において  $\operatorname{Re}(s)$  が  $-\infty \sim 0$ ,  $\operatorname{Im}(s)$  が

$n\omega_s - \frac{\omega_s}{2} \sim n\omega_s + \frac{\omega_s}{2}$  ( $n$  は整数) で切り取られた部分が  $z$  平面の原点 0 を中心と

し半径が  $|z|=1$  となる円の内側に写像される。このことから, 離散時間システムでは, 伝達関数  $H(z)$  (インパルス応答  $h(n)$ ) の極が半径 1 の円の内部に存在する場合に安定動作するといえる。逆に極が 1 つでも円の外部に存在する場合は不安定となる。

連続時間システムにおける伝達関数  $H(s)$  の周波数特性は,  $s = j\omega = j2\pi f$  とす

ることにより求められる。同様に、離散時間システムにおける伝達関数  $H(z)$  の周波数特性は、 $z = e^{j\omega T} = e^{j2\pi \frac{\omega}{\omega_s}} = e^{j2\pi \frac{f}{f_s}}$  とすることにより求められる。

図 8.39 Z 変換の z 平面とラプラス変換の s 平面

### 8.7.5 FIR システムと IIR システム

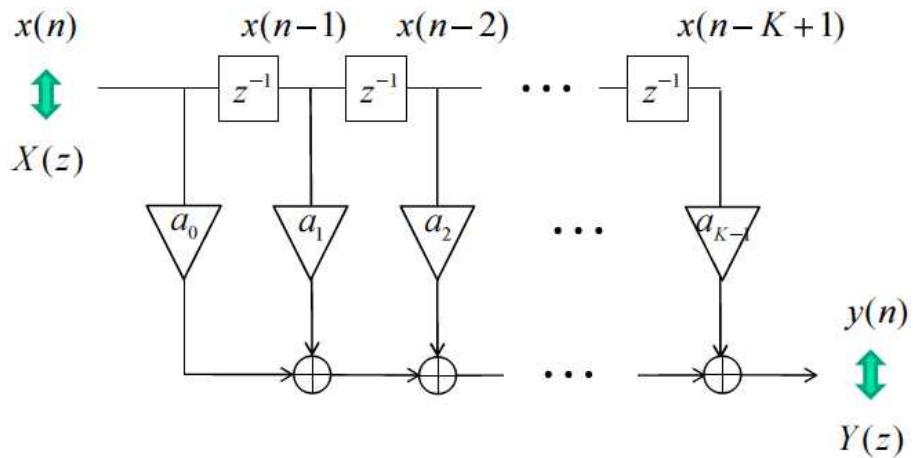

図 8.40 に *FIR* (finite impulse response) システムのブロック図を示す。時間領域および Z 領域の入出力信号関係は次式のように有限個の連続した信号パルスの和で与えられる。

(時間領域)

$$y(n) = \sum_{k=0}^{K-1} a_k x(n-k) = a_0 x(n) + a_1 x(n-1) + \cdots + a_{K-1} x(n-K+1) \quad (8.97)$$

(Z 領域)

$$Y(z) = \sum_{k=0}^{K-1} a_k z^{-k} X(z) = (a_0 + a_1 z^{-1} + \cdots + a_{K-1} z^{-K+1}) X(z) \quad (8.98)$$

図 8.40 FIR(finite impulse response)システムのブロック図

ここで、 $a_0 = a_1 = \dots = a_{K-1} = \frac{1}{K}$  とすると次式となる。これは連続する  $K$  個の信号パルスの移動平均を表わしている。

(時間領域)

$$y(n) = \frac{1}{K} \sum_{k=0}^{K-1} x(n-k) = \frac{1}{K} (x(n) + x(n-1) + \dots + x(n-K+1)) \quad (8.99)$$

(Z 領域)

$$Y(z) = \frac{1}{K} \sum_{k=0}^{K-1} z^{-k} X(z) = \frac{1}{K} (1 + z^{-1} + \dots + z^{-K+1}) X(z) = \frac{1}{K} \frac{1-z^{-K}}{1-z^{-1}} X(z) \quad (8.100)$$

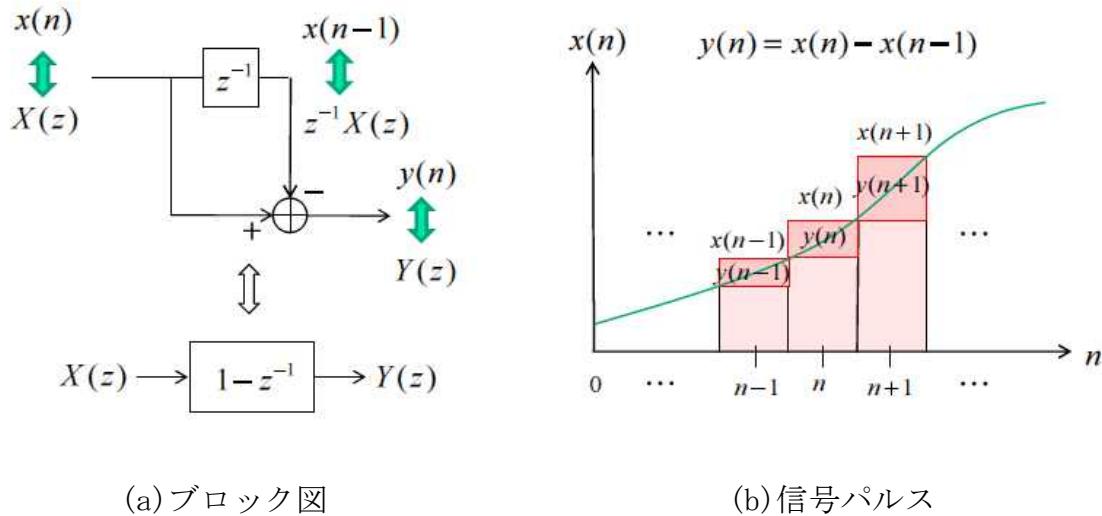

次に、 $a_0 = 1$ ,  $a_1 = -1$ ,  $a_k = 0$  ( $k \neq 0, 1$ ) とすると次式となる。これは微分回路となる。

(時間領域)

$$y(n) = a_0 x(n) + a_1 x(n-1) = x(n) - x(n-1) \quad (8.101)$$

(Z 領域)

$$Y(z) = (1 - z^{-1}) X(z) \quad (8.102)$$

図 8.41 に微分回路の(a)ブロック図および(b)信号パルスを示す。

図 8.41 微分回路の(a)ブロック図および(b)信号パルス

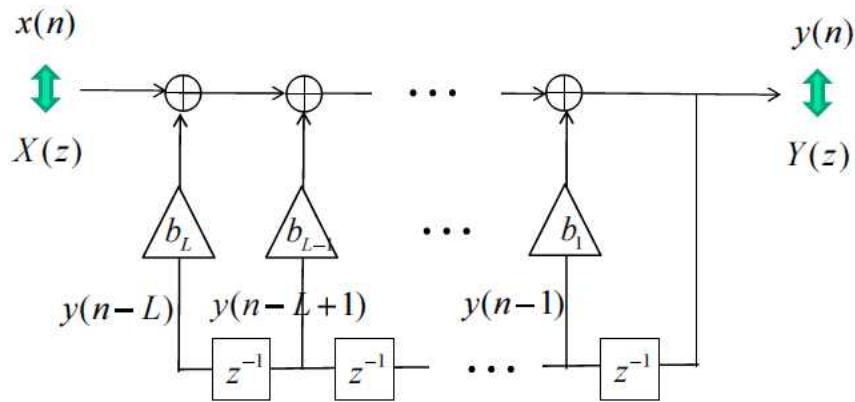

図 8.42 に  $L$  個の帰還パスが存在する IIR (infinite impulse response) システムのブロック図を示す。

図 8.42 IIR (infinite impulse response) システムのブロック図

ここで、特に帰還パスが 1 個で、 $b_1=1$ 、 $b_k=0$  ( $k \neq 1$ ) の場合を考えると、この場合の時間領域およびZ領域の入出力信号関係は次式のように与えられる。これは積分回路となる。

(時間領域)

$$y(n) = x(n) + b_1 y(n-1) = x(n) + y(n-1) \quad (8.103)$$

(Z 領域)

$$\begin{aligned} Y(z) &= X(z) + z^{-1}Y(z) \\ \rightarrow Y(z) &= \frac{1}{1-z^{-1}} X(z) = (1 + z^{-1} + z^{-2} + \dots)X(z) \end{aligned} \quad (8.104)$$

式 (8.104) から、出力信号は無限個の信号パルスの和となっている。これが *IIR* と呼ばれるゆえんである。

### 8.7.7 積分回路による積分回路の構成と動作

時間領域および Z 領域の入出力信号関係が式 (8.103), 式 (8.104) で与えられる回路は積分回路（ここではタイプ 1 の積分回路とよぶ）となっている。

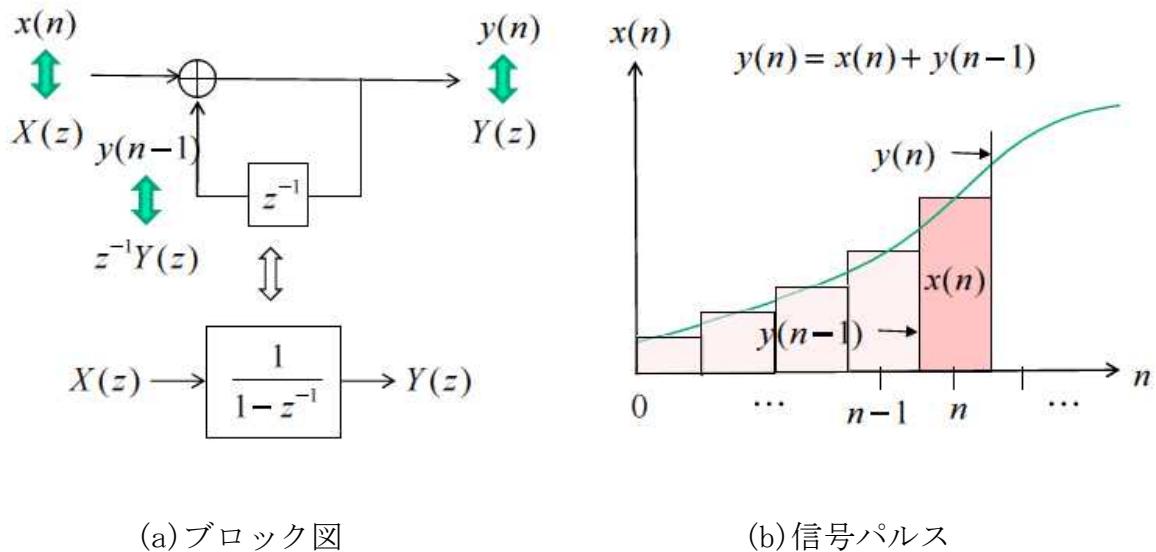

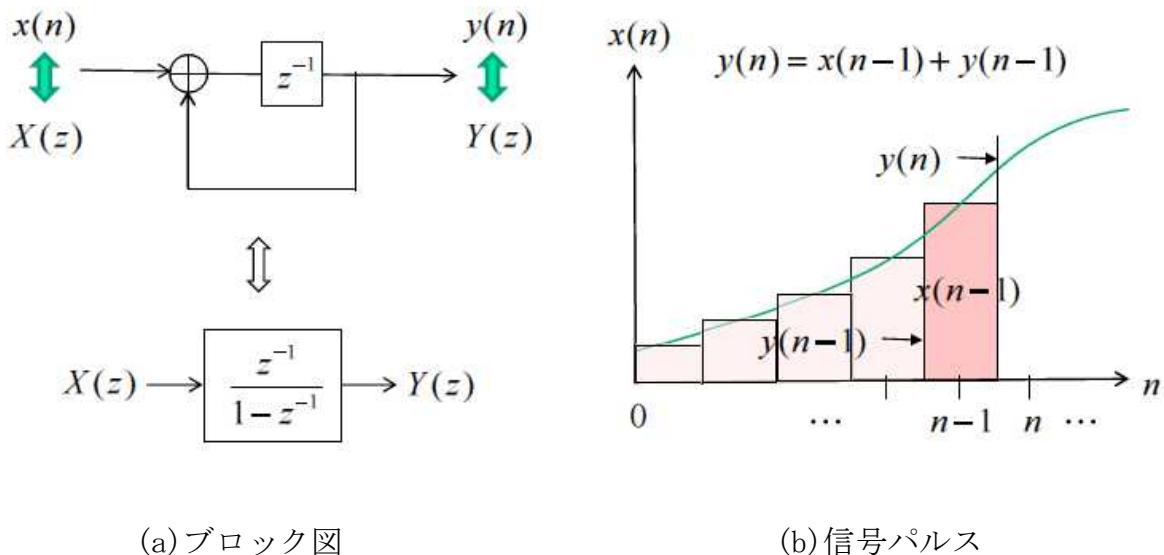

図 8.43 に積分回路（タイプ 1）の(a)ブロック図および(b)信号パルスを示す。

図 8.43 積分回路（タイプ 1）の(a)ブロック図および(b)信号パルス

離散アナログ回路をハードウェア構成するのにスイッチトキャパシタ回路が用いられる。図 8.44 に積分回路（タイプ 1）の離散アナログ回路構成例を示す。

図 8.44 積分回路（タイプ 1）の離散アナログ回路構成例

図 8.44 の回路の動作は以下のように説明される。

オペアンプの性質からオペアンプの入力端  $a$  点は仮想接地点となっている。スイッチを 位相  $\phi_1$  ( $\phi_1$  導通,  $\phi_2$  開放) とすると, 容量  $C_1$  に電荷  $Q_1(n) = C_1(-x(n))$  が

図の極性の向きでチャージされる。電荷保存則から, 容量  $C_2$  にも電荷は転送さ

れ,  $C_2$  にあらかじめ存在した容量  $Q_2(n-1)$  に加算され (図の極性の場合は減算

され), 次式で与えられる電荷  $Q_2(n)$  が生じる。

$$Q_2(n) = -Q_1(n) + Q_2(n-1) = -C_1(-x(n)) + C_2y(n-1) \quad (8.105)$$

この  $Q_2(n)$  により, 次式で与えられる  $y(n)$  が生じる。

$$Q_2(n) = C_2y(n) \quad (8.106)$$

次にスイッチを 位相  $\phi_2$  ( $\phi_2$  導通,  $\phi_1$  開放) とすると, 容量  $C_1$  の電荷は 0 にリセ

ットされる。容量  $C_2$  の電荷はそのまま保持される。ここで, 容量  $C_1 = C_2 = C$  と

すると, 式 (8.105), (8.106) から次式が得られる。

$$y(n) = x(n) + y(n-1) \quad (8.107)$$

これを  $Z$  変換すると次式が得られる。

$$\begin{aligned} Y(z) &= X(z) + z^{-1}Y(z) \\ \rightarrow Y(z) &= \frac{1}{1-z^{-1}}X(z) \end{aligned} \quad (8.108)$$

これらの式は、先に与えた式 (8.103), (8.104) と等しくなっている。

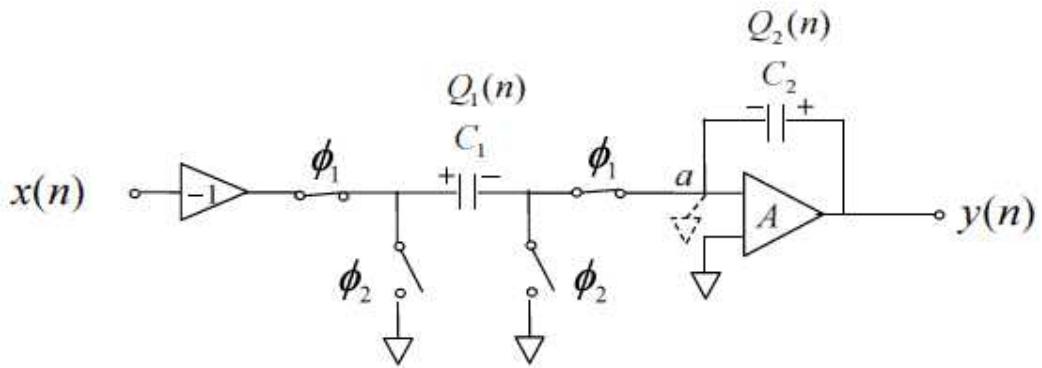

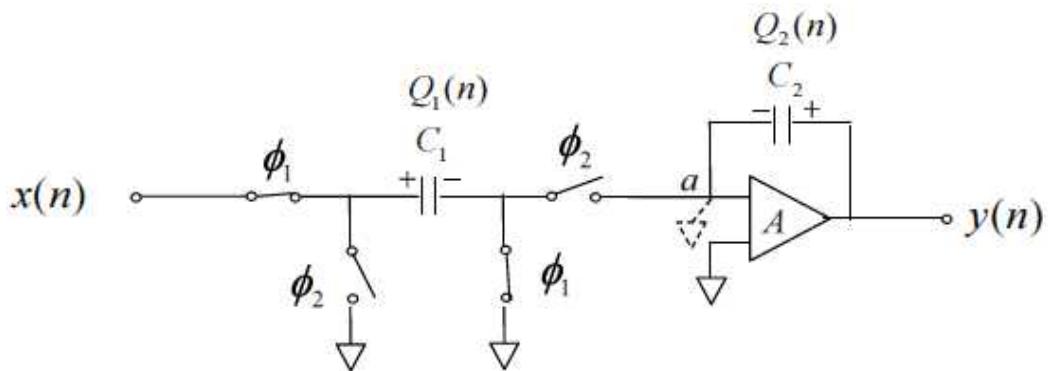

離散アナログ回路で積分回路を構成する場合、図 8.45 に示す積分回路（ここではタイプ 2 の積分回路とよぶ）も用いられる。

図 8.45 積分回路（タイプ 2）の(a)ブロック図および(b)信号パルス

この場合、時間領域および  $Z$  領域の入出力信号関係は次式で与えられる。

(時間領域)

$$y(n) = x(n-1) + y(n-1) \quad (8.109)$$

( $Z$  領域)

$$Y(z) = \frac{z^{-1}}{1-z^{-1}}X(z) \quad (8.110)$$

図 8.46 に積分回路（タイプ 2）の離散アナログ回路構成例を示す。

図 8.46 積分回路（タイプ 2）の離散アナログ回路構成例

図 8.46 の回路の動作は以下のように説明される。

スイッチを 位相  $\phi_1$  とすると、容量  $C_1$  に電荷  $Q_1(n) = C_1 x(n)$  が図の極性の向きでチャージされる。一方、容量  $C_2$  には電荷  $Q_2(n) = C_2 y(n)$  が図の極性の向きでチャージされている。次にスイッチを 位相  $\phi_2$  とすると、容量  $C_1$  の電荷は 0 になり、電荷保存則から、容量  $C_2$  に電荷が転送される。図の極性の場合、転送された電荷は  $C_2$  にあらかじめ存在した容量  $Q_2(n-1)$  に加算され、次式で与えられる電荷  $Q_2(n)$  が生じる。

$$Q_2(n) = Q_1(n-1) + Q_2(n-1) = C_1 x(n-1) + C_2 y(n-1) \quad (8.111)$$

この  $Q_2(n)$  により、次式で与えられる  $y(n)$  が生じる。

$$Q_2(n) = C_2 y(n) \quad (8.112)$$

ここで、容量  $C_1 = C_2 = C$  とすると、式 (8.111), (8.112) から次式が得られる。

$$y(n) = x(n-1) + y(n-1) \quad (8.113)$$

これを Z 変換すると次式が得られる。

$$\begin{aligned} Y(z) &= z^{-1}X(z) + z^{-1}Y(z) \\ \rightarrow \quad Y(z) &= \frac{z^{-1}}{1-z^{-1}} X(z) \end{aligned} \quad (8.114)$$

これらの式は、先に与えた式 (8.109), (8.110) と等しくなっている。

## 8.8 $\Delta \Sigma$ 変調 ADC/DAC

### 8.8.1 概要

ADC/DAC の量子化雑音による  $SNR_q$  は、オーバサンプル比  $OSR$  に比例して増大（改善）する（式 (8.16), (8.17) 参照）。 $OSR$  を増大して行くことにより、1 ビット量子化 ( $b=1$ ) でも十分な  $SNR_q$  性能を得ることができないだろうか？との期待が出てくる。しかし、単純に  $OSR$  を増大するだけでこれを行うには非現実的なレベルまで  $OSR$  を増大させる必要があり不可能である。これに対して、 $\Delta \Sigma$  変調 ADC/DAC では量子化雑音の周波数特性の形を変化させるノイズシェーピング機能により、現実的な  $OSR$  の値であっても 1 ビット量子化 ADC/DAC が実現可能となる。

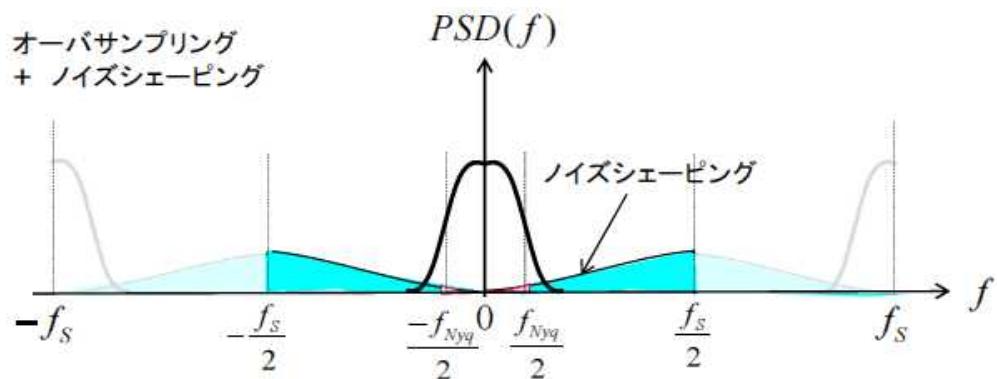

図 8.47 に  $\Delta \Sigma$  変調によるノイズシェーピングの効果を模式的に示す。図の (a) は比較のために示したオーバサンプリングのみを用いるもの、(b) はオーバサンプリングと  $\Delta \Sigma$  変調によるノイズシェーピングを用いるものである。

(a) オーバサンプリングのみ

(b) オーバサンプリング+ノイズシェーピング

図 8.47  $\Delta \Sigma$  変調によるノイズシェーピング効果

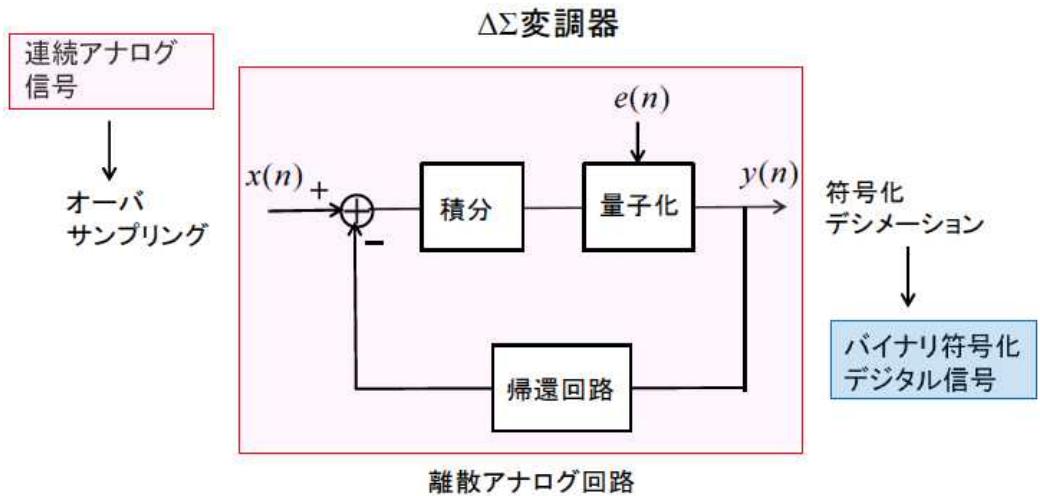

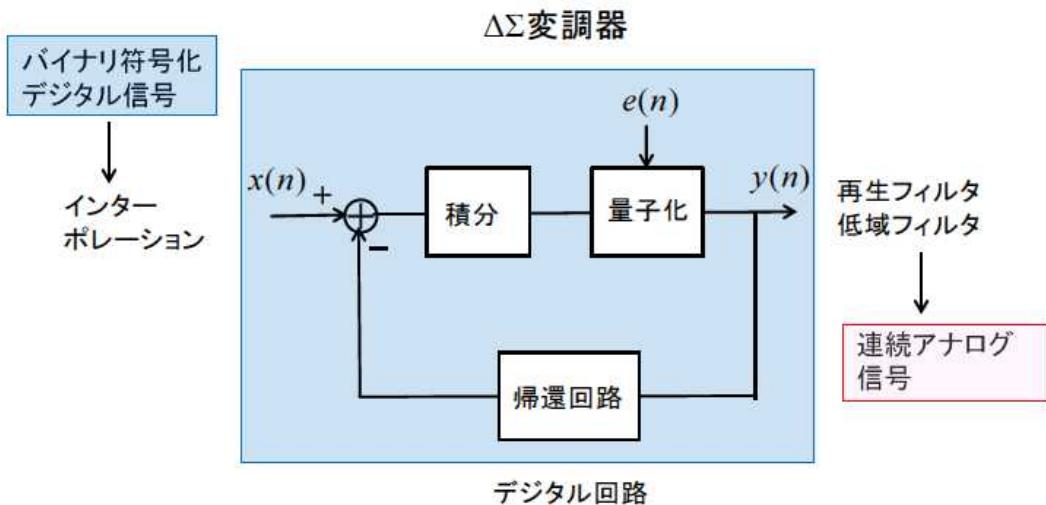

図 8.48 に (a)  $\Delta \Sigma$  変調 ADC および (b)  $\Delta \Sigma$  変調 DAC の構成ブロック図を示す。 $\Delta \Sigma$  変調器部分の回路構成要素は (a), (b) とも同じであるが、(a) ADC 用  $\Delta \Sigma$  変調器は離散アナログ回路（具体的にはスイッチトキャパシタ回路）で構成されるのに対して、(b) DAC 用  $\Delta \Sigma$  変調器はデジタル回路で構成される。

(a)  $\Delta \Sigma$  変調 ADC

(b)  $\Delta \Sigma$  変調 DAC

図 8.48  $\Delta \Sigma$  変調 ADC/DAC の構成ブロック図

### 8.8.2 $\Delta \Sigma$ 変調器によるノイズシェーピング

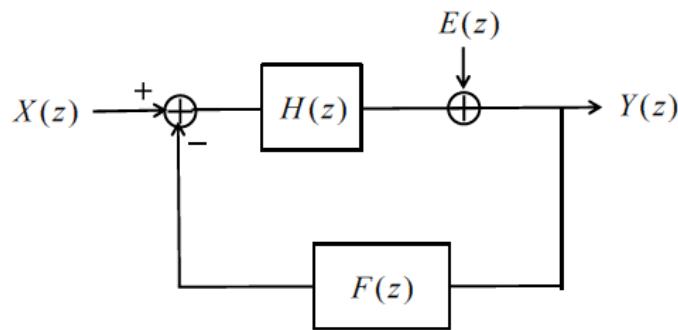

図 8.49 に  $z$  パラメータを用いて表わした一般化された  $\Delta \Sigma$  変調器の解析モデルを示す。図において、 $X(z)$  は入力信号（電圧）、 $Y(z)$  は量子化された出力信号（電圧）、 $E(z)$  は量子化誤差（電圧）、 $H(z)$  は積分回路の伝達関数、 $F(z)$  は帰還回路の伝達関数である。この時、 $Y(z)$  は以下で与えられる。

$$Y(z) = H(z)(X(z) - F(z)Y(z)) + E(z)$$

$$\begin{aligned} \rightarrow Y(z) &= \frac{H(z)}{1+H(z)F(z)} X(z) + \frac{1}{1+H(z)F(z)} E(z) \\ &= STF(z)X(z) + NTF(z)E(z) \end{aligned} \quad (8.115)$$

ここで、

$STF(z)$  : 信号伝達関数

$NTF(z)$  : 雑音伝達関数

図 8.49 一般化された  $\Delta\Sigma$  変調器の解析モデル

$\Delta\Sigma$  変調器の積分回路として、前節で述べたタイプ 1 またはタイプ 2 の積分回路を用いることができる。

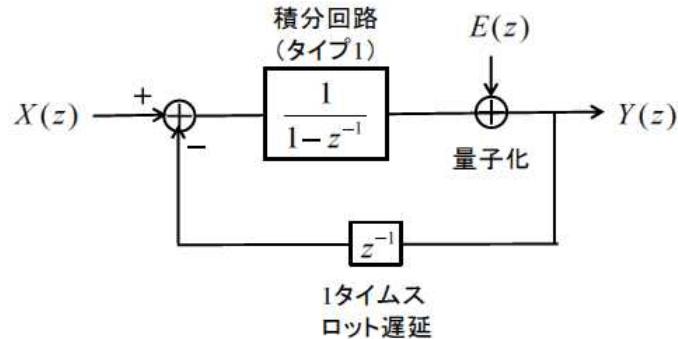

まず、タイプ 1 の積分回路を用いる場合について述べる。図 8.50 に  $z$  パラメータを用いて表わした  $\Delta\Sigma$  変調器のブロック図を示す。

図 8.50  $z$  パラメータを用いて表わした  $\Delta\Sigma$  変調器のブロック図

— 積分回路 (タイプ 1) を用いる場合 —

この場合、式 (5.115) の  $Y(z)$ ,  $STF(z)$ ,  $NTF(z)$  は以下となる。

$$\begin{aligned} Y(z) &= STF(z)X(z) + NTF(z)E(z) \\ &= X(z) + (1 - z^{-1})E(z) \end{aligned} \quad (8.116)$$

$X(z)$  と  $E(z)$  は無相関であることから、電力スペクトルを与える  $|Y(z)|^2$  は次式で与えられる。

$$|Y(z)|^2 = |X(z)|^2 + |1 - z^{-1}|^2 |E(z)|^2 \quad (8.117)$$

ここで、 $z^{-1} = e^{-j2\pi f/f_s}$  の関係を用いると  $|1 - z^{-1}|^2$  は以下のようになり、

$$|1 - z^{-1}|^2 = \left| 1 - e^{-j2\pi f/f_s} \right|^2 = 4 \sin^2 \left( \pi \frac{f}{f_s} \right) \quad (8.118)$$

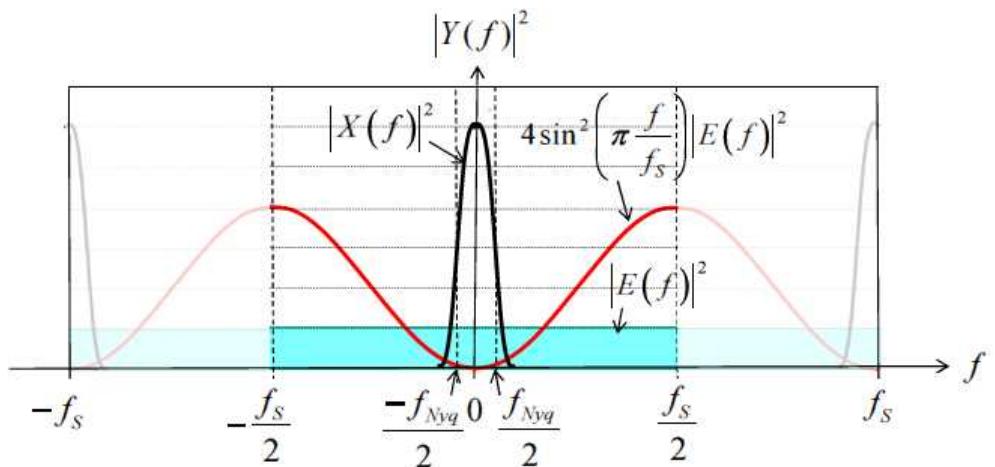

これから、 $|Y(f)|^2$  は以下で与えられる。

$$\begin{aligned} |Y(f)|^2 &= |X(f)|^2 + 4 \sin^2 \left( \pi \frac{f}{f_s} \right) |E(f)|^2 \\ \text{信号スペクトラム} &\qquad \text{量子化雑音スペクトラム} \end{aligned} \quad (8.119)$$

図 8.51 に電力スペクトル  $|Y(f)|^2$  特性を示す。 $\Delta \Sigma$  変調器によるノイズシェーピングにより、信号帯域内の量子化雑音電力が低減されている。

図 8.51 電力スペクトル密度 $|Y(f)|^2$ 特性

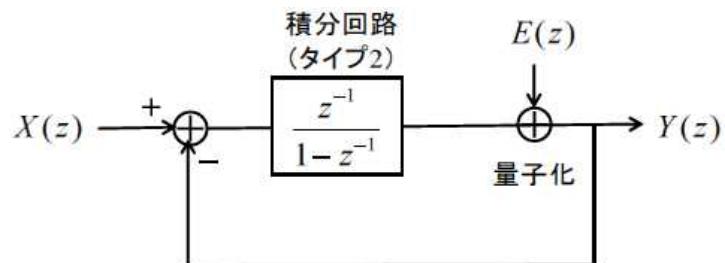

次に、タイプ2の積分回路を用いる場合について述べる。図8.52に $z$ パラメータを用いて表わした $\Delta\Sigma$ 変調器のブロック図を示す。

図 8.52  $z$ パラメータを用いて表わした $\Delta\Sigma$ 変調器のブロック図

— 積分回路（タイプ2）を用いる場合 —

この場合、式(8.115)の $Y(z)$ ,  $STF(z)$ ,  $NTF(z)$ は以下となる。

$$\begin{aligned} Y(z) &= STF(z)X(z) + NTF(z)E(z) \\ &= z^{-1}X(z) + (1-z^{-1})E(z) \end{aligned} \tag{8.120}$$

$z^{-1} = e^{-j2\pi f/f_s}$  とすると $|Y(f)|^2$ は以下の様に求まる。

$$\begin{aligned}

|Y(f)|^2 &= \left| e^{-j2\pi f/f_s} \right|^2 |X(f)|^2 + 4 \sin^2 \left( \pi \frac{f}{f_s} \right) |E(f)|^2 \\

&= |X(f)|^2 + 4 \sin^2 \left( \pi \frac{f}{f_s} \right) |E(f)|^2

\end{aligned} \tag{8. 121}$$

以上から、積分回路（タイプ1）を用いる場合と積分回路（タイプ2）を用いる場合で、 $Y(z)$ は式の形が異なるが（式（8. 116）と式（8. 120）），電力スペクトル $|Y(f)|^2$ は、両者で等しくなる（式（8. 119）と式（8. 121））。

次に、ノイズシェーピングによる $SNR_q$ の改善効果について述べる。信号帯域内の量子化雑音に対する等価雑音電力 $P_{Nq,eff}$ は次式で与えられる。

$$P_{Nq,eff} = \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} 4 \sin^2 \left( \pi \frac{f}{f_s} \right) |E(f)|^2 df = 4 \frac{P_{Nq}}{f_s} \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} \sin^2 \left( \pi \frac{f}{f_s} \right) df \tag{8. 122}$$

ここで、 $|E(f)|^2 = N_q = \frac{P_{Nq}}{f_s}$ を用いた（式（8. 13）参照）。

ここで、OSRが十分大きく $f \ll f_s$ の場合、以下の近似が成り立つ

$$P_{Nq,eff} \approx 4 \frac{P_{Nq}}{f_s} \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} \left( \pi \frac{f}{f_s} \right)^2 df = \frac{\pi^2 P_{Nq}}{3} \left( \frac{f_{Nyq}}{f_s} \right)^3 = \frac{\pi^2 P_{Nq}}{3 \cdot OSR^3} \tag{8. 123}$$

これから、 $\Delta\Sigma$ 変調器によりノイズシェーピングした時の $SNR_q$ は次式で与えられる。

$$SNR_q = \frac{P_s}{P_{Nq,eff}} = \frac{3 \cdot OSR^3}{\pi^2} \frac{P_s}{P_{Nq}} \tag{8. 124}$$

オーバサンプリングのみの場合の  $SNR_q$  (これを  $SNR_{q,0}$  とする) の式 (8.16) を以下に再掲する。

$$SNR_{q,0} = OSR \frac{P_S}{P_{Nq}} \quad (8.125) \quad ((8.16) \text{と同じ})$$

オーバサンプリングのみによる  $SNR$  の改善効果は  $OSR$  倍であったが、1 次  $\Delta \Sigma$  変調器<sup>注\*1</sup>によりノイズシェーピングした時の  $SNR$  の改善効果は  $\frac{3 \cdot OSR^3}{\pi^2}$  倍に増大する。

注\*1 後述する高次  $\Delta \Sigma$  変調器に対し、図 8.50、図 8.52 に示した  $\Delta \Sigma$  変調器は 1 次  $\Delta \Sigma$  変調器とよばれる。

### 8.8.3 $\Delta \Sigma$ 変調器の離散アナログ回路構成と動作

ここでは、上で述べた ADC 用  $\Delta \Sigma$  変調器を離散アナログ回路で構成する場合の回路構成とその動作について述べる、

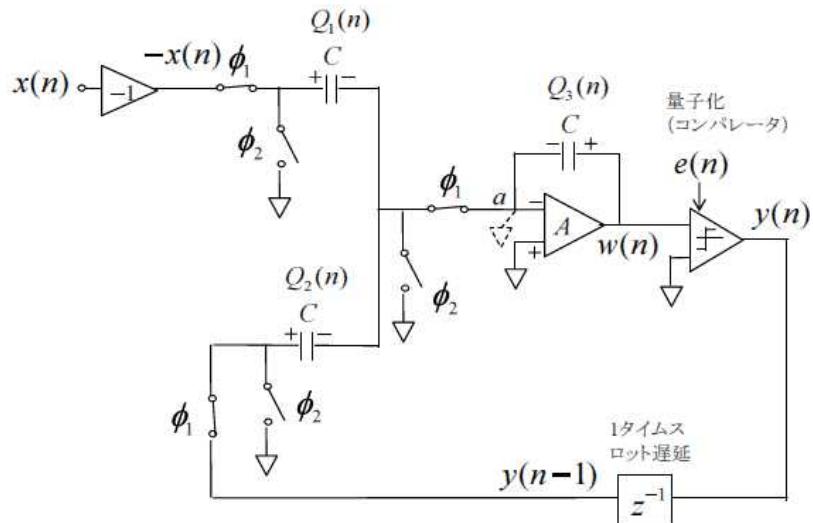

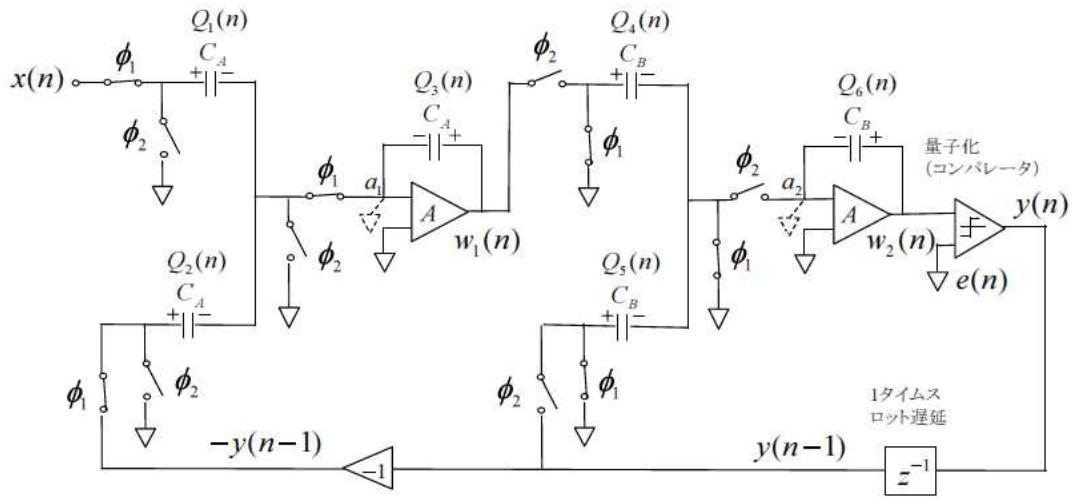

まず、積分回路（タイプ 1）を用いる場合について述べる。図 8.53 は積分回路（タイプ 1）を用いる場合の ADC 用  $\Delta \Sigma$  変調器の回路構成例である。

図 8.53 ADC 用  $\Delta \Sigma$  変調器の回路構成例

(積分回路（タイプ 1）を用いる場合)

図 8.53 の回路動作は以下のように説明される。

I 位相  $\phi_1$  の時

$$\begin{aligned} Q_1(n) &= -Cx(n) & Q_2(n) &= Cy(n-1) \\ Q_3(n) &= -Q_1(n) - Q_2(n) + Q_3(n-1) & = Cx(n) - Cy(n-1) + Cw(n-1) &= Cw(n) \\ \rightarrow w(n) &= x(n) - y(n-1) + w(n-1) \end{aligned} \quad (8.126)$$

II 位相  $\phi_2$  の時は容量  $Q_1(n)$ ,  $Q_2(n)$  のリセットを行っている。

III  $y(n)$ ,  $w(n)$ ,  $e(n)$  の関係

$$y(n) = w(n) + e(n) \quad (8.127)$$

式 (8.126), (8.127) を  $Z$  変換すると

$$W(z) = X(z) - z^{-1}Y(z) + z^{-1}W(z) \quad (8.128)$$

$$Y(z) = W(z) + E(z) \quad (8.129)$$

式 (8.128), (8.129) から  $W(z)$  を消去すると

$$Y(z) = X(z) + (1 - z^{-1})E(z) \quad (8.130)$$

上式は、積分回路（タイプ 1）を用いた  $\Delta \Sigma$  変調器の場合の式 (8.116) と等しくなっている。

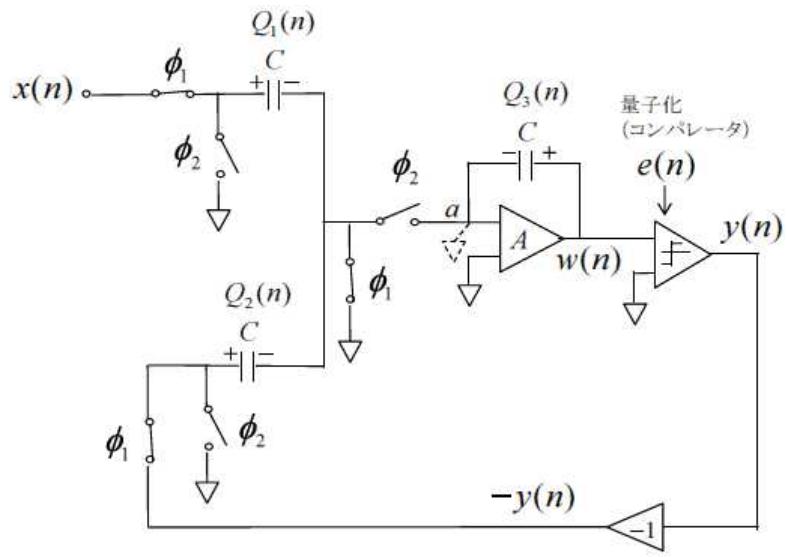

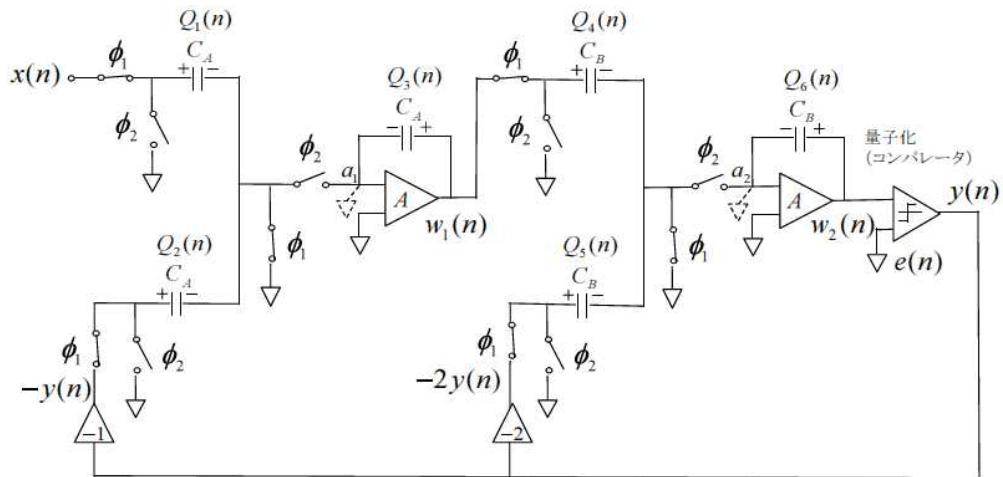

次に、積分回路（タイプ 2）を用いる場合について述べる、図 8.54 は積分回路（タイプ 2）を用いる場合の ADC 用  $\Delta \Sigma$  変調器の回路構成例である。

図 8.54 ADC 用  $\Delta \Sigma$  変調器の回路構成例

(積分回路 (タイプ 2) を用いる場合)

図 8.54 の回路動作は以下のように説明される。

### I 位相 $\phi_1$ の時

$$Q_1(n) = Cx(n) \quad Q_2(n) = -Cy(n) \quad Q_3(n) = Cw(n)$$

### II 位相 $\phi_2$ の時

$$Q_1(n) = 0 \quad Q_2(n) = 0$$

$$\begin{aligned} Q_3(n) &= Q_1(n-1) + Q_2(n-1) + Q_3(n-1) \\ &= Cx(n-1) - Cy(n-1) + Cw(n-1) = Cw(n) \end{aligned}$$

$$\rightarrow w(n) = x(n-1) - y(n-1) + w(n-1) \quad (8.131)$$

### III $y(n)$ , $w(n)$ , $e(n)$ の関係

$$y(n) = w(n) + e(n) \quad (8.132)$$

式 (8.131), (8.132) を  $Z$  変換すると

$$W(z) = z^{-1}X(z) - z^{-1}Y(z) + z^{-1}W(z) \quad (8.133)$$

$$Y(z) = W(z) + E(z) \quad (8.134)$$

式 (8.133), (8.134) から  $W(z)$  を消去すると

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z) \quad (8.135)$$

上式は、積分回路（タイプ 2）を用いた  $\Delta \Sigma$  変調器の場合の式 (8.120) と等しくなっている。

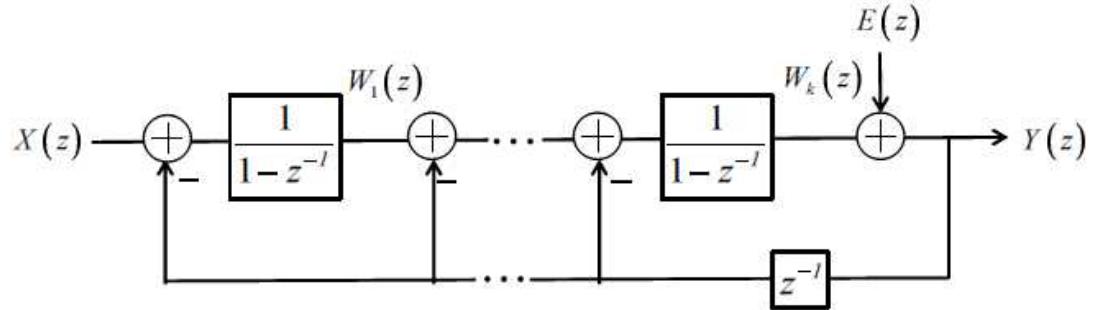

#### 8.8.4 高次 $\Delta \Sigma$ 変調器によるノイズシェーピングの高度化

$\Delta \Sigma$  変調器によるノイズシェーピングの効果を増大させるために高次の  $\Delta \Sigma$  変調器がある。図 8.55 に帰還ループを用いる構成の高次  $\Delta \Sigma$  変調器の解析モデルを示す（ここでは次数を  $k$  としている）。

図 8.55 帰還ループを用いる構成の高次  $\Delta \Sigma$  変調器の解析モデル

図中の  $W_k(z)$  は次式で表わすことができる。

$$\begin{aligned} W_k(z) &= \frac{1}{(1-z^{-1})^k} X(z) - \left( \frac{1}{(1-z^{-1})^k} + \cdots + \frac{1}{(1-z^{-1})^2} + \frac{1}{(1-z^{-1})} \right) z^{-1} Y(z) \\ &= \frac{1}{(1-z^{-1})^k} X(z) + \left( 1 - \frac{1}{(1-z^{-1})^k} \right) Y(z) \end{aligned} \quad (8.136)$$

$Y(z)$  は  $W_k(z)$  と以下の関係がある。

$$Y(z) = W_k(z) + E(z) \quad (8.137)$$

式 (8.136), (8.137) から次式が得られる。

$$Y(z) = X(z) + (1 - z^{-1})^k E(z) \quad (8.138)$$

ここで,  $z^{-1} = e^{-j2\pi f/f_s}$  とすると  $|Y(f)|^2$  は以下の様に求まる。

$$|Y(f)|^2 = |X(f)|^2 + 4^k \sin^{2k} \left( \pi \frac{f}{f_s} \right) |E(f)|^2 \quad (8.139)$$

信号帯域内の量子化雑音に対する等価雑音電力  $P_{Nq,eff}$  は

$$P_{Nq,eff} = \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} 4^k \sin^{2k} \left( \pi \frac{f}{f_s} \right) |E(f)|^2 df = 4^k \frac{P_{Nq}}{f_s} \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} \sin^{2k} \left( \pi \frac{f}{f_s} \right) df \quad (8.140)$$

さらに,  $f \ll f_s$  であるから, 以下の近似が成り立つ

$$P_{Nq,eff} \approx 4^k \frac{P_{Nq}}{f_s} \int_{-\frac{f_{Nyq}}{2}}^{\frac{f_{Nyq}}{2}} \left( \pi \frac{f}{f_s} \right)^{2k} df = \frac{\pi^{2k} P_{Nq}}{2k+1} \left( \frac{f_{Nyq}}{f_s} \right)^{2k+1} = \frac{\pi^{2k} P_{Nq}}{2k+1} \left( \frac{1}{OSR} \right)^{2k+1} \quad (8.141)$$

これから,  $k$  次  $\Delta \Sigma$  変調によりノイズシェーピングした時の  $SNR_q$  は次式で与えられる。

$$SNR_q = \frac{P_s}{P_{Nq,eff}} = \frac{(2k+1) \cdot OSR^{2k+1}}{\pi^{2k}} \frac{P_s}{P_{Nq}} \quad (8.142)$$

$SNR$  の改善効果は  $\frac{(2k+1) \cdot OSR^{2k+1}}{\pi^{2k}}$  倍に増大している。

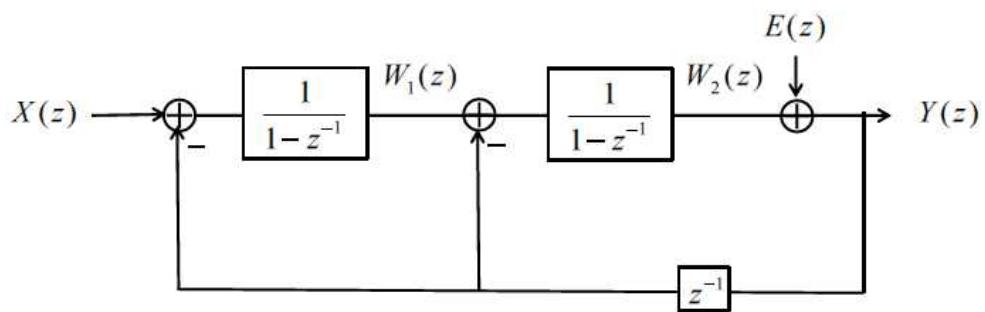

以下において、帰還ループを用いた構成の 2 次  $\Delta \Sigma$  変調器について述べる。

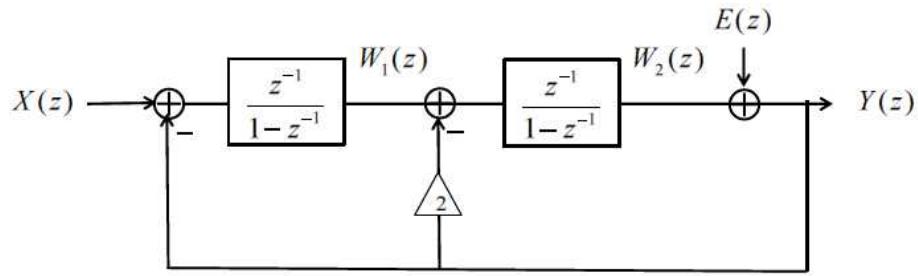

図 8.56 に積分回路（タイプ 1）を用いた 2 次  $\Delta \Sigma$  変調器の  $z$  パラメータを用いて表わしたブロック図を示す。

図 8.56  $z$  パラメータを用いて表わした 2 次  $\Delta \Sigma$  変調器のブロック図

— 積分回路（タイプ 1）を用いた場合 —

図中の  $W_2(z)$ ,  $Y(z)$  はそれぞれ以下で表わすことができる。

$$\begin{aligned} W_2(z) &= \frac{1}{(1-z^{-1})^2} X(z) - \left( \frac{1}{(1-z^{-1})^2} + \frac{1}{(1-z^{-1})} \right) z^{-1} Y(z) \\ &= \frac{1}{(1-z^{-1})^2} X(z) - \frac{(2-z^{-1})z^{-1}}{(1-z^{-1})^2} Y(z) \end{aligned} \quad (8.143)$$

$$Y(z) = W_2(z) + E(z) \quad (8.144)$$

式 (8.143), (8.144) から,  $W_2(z)$  を消去して  $Y(z)$  に対する次式が得られる。

$$Y(z) = X(z) + (1-z^{-1})^2 E(z) \quad (8.145)$$

図 8.57 に積分回路（タイプ 1）を用いた 2 次  $\Delta \Sigma$  変調器の離散アノログ回路構成例を示す。

図 8.57 2 次  $\Delta \Sigma$  変調器の離散アナログ回路構成例

— 積分回路（タイプ 1）を用いた場合 —

図 8.58 に積分回路（タイプ 2）を用いた 2 次  $\Delta \Sigma$  変調器の  $z$  パラメータを用いて表わしたブロック図を示す。

図中の  $W_2(z)$ ,  $Y(z)$  はそれぞれ以下で表わすことができる。

$$\begin{aligned} W_2(z) &= \left( \frac{z^{-1}}{1-z^{-1}} \right)^2 X(z) - \left( \left( \frac{z^{-1}}{1-z^{-1}} \right)^2 + \frac{2z^{-1}}{1-z^{-1}} \right) Y(z) \\ &= \left( \frac{z^{-1}}{1-z^{-1}} \right)^2 X(z) - \frac{2z^{-1}-z^{-2}}{(1-z^{-1})^2} Y(z) \end{aligned} \quad (8.146)$$

$$Y(z) = W_2(z) + E(z) \quad (8.147)$$

上式 (8.146), (8.147) から,  $W_2(z)$  を消去して  $Y(z)$  に対する次式が得られる。

$$Y(z) = z^{-2}X(z) + (1-z^{-1})^2 E(z) \quad (8.148)$$

図 8.58  $z$  パラメータを用いて表わした 2 次  $\Delta \Sigma$  変調器のブロック図

— 積分回路（タイプ 2）を用いた場合 —

図 8.59 に積分回路（タイプ 2）を用いた 2 次  $\Delta \Sigma$  変調器の離散アナログ回路構成例を示す。

図 8.59 2 次  $\Delta \Sigma$  変調器の離散アナログ回路構成例

— 積分回路（タイプ 2）を用いた場合 —

$\Delta \Sigma$  変調器の高次化はノイズシェーピング効果を大きくする上で極めて重要なと言える。ここで述べた帰還ループを用いる構成の  $\Delta \Sigma$  変調器では 2 次まで実現されている。しかし、それ以上の高次化は帰還ループによる不安定動作のため実現困難である。このため、それ以上の高次の  $\Delta \Sigma$  変調器は後述するカスケード接続（MASH 方式）構成などを用いて実現されている。

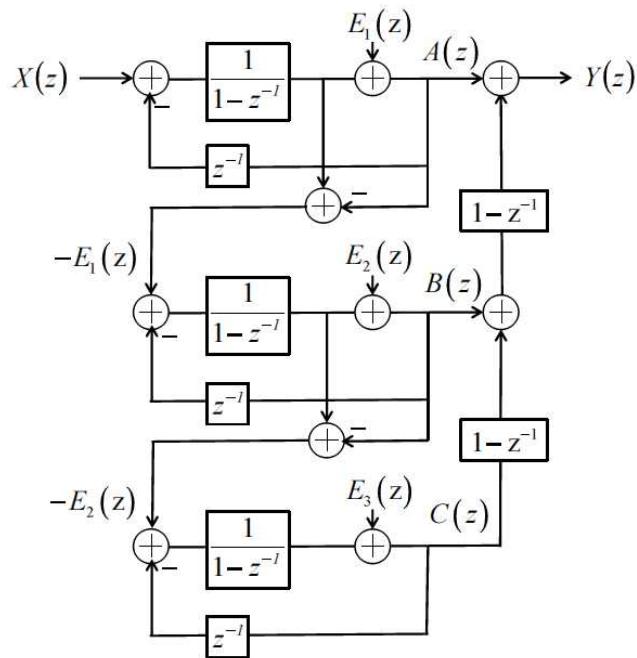

図 8.60 にカスケード接続された（MASH 方式）3 次  $\Delta \Sigma$  変調器の  $z$  パラメータを用いて表わしたブロック図を示す。

図 8.60 カスケード接続 (MASH 方式) 3 次  $\Delta \Sigma$  変調器のブロック図

伝達関数を以下で導出する。

図中の  $A(z)$ ,  $B(z)$ ,  $C(z)$  は、タイプ 1 の積分回路を用いた 1 次  $\Delta \Sigma$  変調器の伝達関数（式 (8.116) 参照）の結果を用いて、次式で与えられる。

$$\left. \begin{aligned} A(z) &= X(z) + (1-z^{-1})E_1(z) \\ B(z) &= -E_1(z) + (1-z^{-1})E_2(z) \\ C(z) &= -E_2(z) + (1-z^{-1})E_3(z) \end{aligned} \right\} \quad (8.149)$$

また、 $Y(z)$  は次式で与えられる。

$$Y(z) = A(z) + (1-z^{-1})B(z) + (1-z^{-1})^2C(z) \quad (8.150)$$

式 (8.149), (8.150) から、 $A(z)$ ,  $B(z)$ ,  $C(z)$  を消去し、 $Y(z)$  について解く

と次式が得られる

$$Y(z) = X(z) + (1 - z^{-1})^3 E_3(z) \quad (8.151)$$

3次 $\Delta\Sigma$ 変調器のノイズシェーピング特性が得られている。